La figura 5.4.b presenta una versión mejorada del repetidor de corriente que minimiza el efecto de las corrientes de polarización de base a través del transistor  $Q_B$ . En este circuito se verifica que

$$I_{ref} = I_{C1} + \frac{NI_B}{1 + {}^{\circ}} \tag{5.8}$$

resultando que

$$I_{o} = \frac{I_{ref}}{1 + \frac{N}{°(1 + °)}} = \frac{\frac{V_{CC} \quad 2V_{BE}}{R}}{1 + \frac{N}{°(1 + °)}}$$

(5.9)

En el denominador de la ecuación 5.9, N se encuentra dividido por  $\beta(\beta+1)H\beta^2$  (si  $\beta>>1$ ) frente a  $\beta$  en la ecuación 5.7. Como resultado, el circuito de la figura 5.4.b funciona correctamente con  $\beta$  pequeñas y admite un número mayor de salidas.

## 5.3.- Fuentes de corriente simples FET

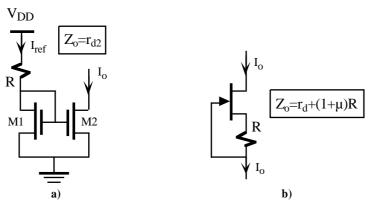

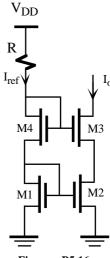

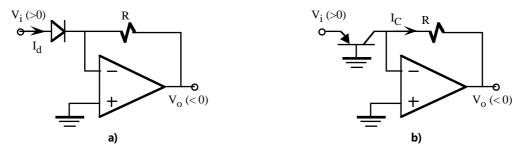

Los espejos de corriente basados en transistores bipolares pueden ser extendidas a transistores FET pero con las propias particularidades de este tipo de dispositivos. Al ser los transistores FET dispositivos controlados por tensión, no presentan los problemas de polarización de base de los bipolares. Sin embargo, la relación cuadrática entre la  $I_D$  y la  $V_{GS}$  dificulta su análisis. La figura 5.5.a muestra una fuente de corriente simple basada en un espejo de corriente constituida por transistores NMOS. El valor de la intensidad de referencia  $I_{ref}$ , que es idéntica a la intensidad de drenador del transistor M1, se obtiene resolviendo el siguiente sistema de ecuaciones:

$$\int_{1}^{\lambda} I_{ref} = I_{D1} = -\left(V_{GS12} V_{T}\right)^{2} = \frac{k}{2} \left(\frac{W}{L}\right)_{1} \left(V_{GS1} V_{T}\right)^{2} \\

\left(V_{DD} = I^{ref} R + V^{GS1}\right) \tag{5.10}$$

Figura 5.5. a) Espejo de corriente basado en un NMOS. b) Fuente de corriente simple con JFET.

En esta fuente de corriente se verifica que  $V_{GS1}=V_{GS2}$ . Si ambos transistores son idénticos y únicamente difieren en la relación (W/L), entonces la relación entre las intensidades de ambos transistores es

$$\frac{I_{D1}}{I_{D2}} = \frac{I}{rI_0} = \frac{(W/L)_1}{(W/L)_2}$$

e

f

(5.11)

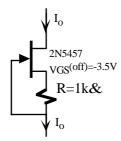

El circuito de la figura 5.5.b corresponde a una fuente de corriente simple basada en un JFET. La tensión en R proporciona la polarización necesaria para que el transistor trabaje en la zona de saturación. La corriente de salida se obtiene resolviendo las siguientes ecuaciones

$$\begin{vmatrix}

I_{O} = I_{D} = I_{DSS} & V_{GS} \\

V_{GS} = I_{O}R

\end{vmatrix}^{2}$$

(5.12)

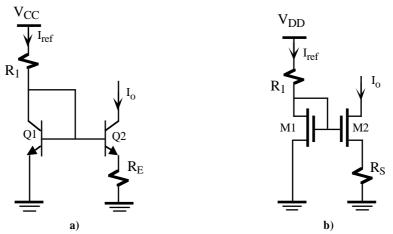

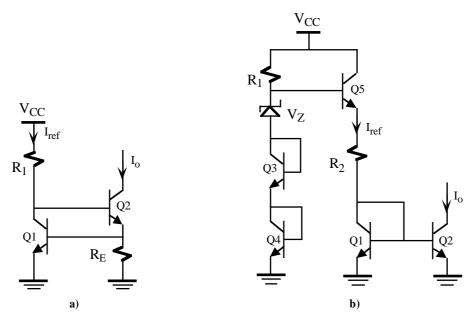

## 5.4.- Fuente de corriente Widlar

En muchos amplificadores integrados se requieren fuentes de corriente con niveles de polarización muy bajos (del orden de 5µA) y alta impedancia de salida. Generar estos valores con fuentes de corriente basadas en espejos de corriente exige que la resistencia de polarización sea del orden de 600k&; estas resistencias son muy costosas de integrar porque ocupan demasiada área. Estos valores de corriente se pueden generar con un coste más bajo en la fuente de corriente Widlar, cuya estructura se muestra en la figura 5.6.a. Esta fuente utiliza una resistencia de emisor de pequeño valor de forma que los transistores están trabajando con diferentes valores de  $V_{\rm BE}$ .

Figura 5.6. Fuente de corriente Widlar basada en a) transistores bipolares y b) MOSFET.

En este circuito, si se suma las tensiones en la base de los transistores, y asumiendo que  $\beta >>1$ , se obtiene

$$V_{BE1} V_{BE2} I_{C2}R_E = 0$$

(5.13)

Sustituyendo las tensiones  $V_{BE}$  por las expresiones de las ecuaciones de Ebers-Moll indicadas en la ecuación 5.1 y suponiendo transistores idénticos  $I_{S1}=I_{S2}=I_{S}$ , resulta

$$V_T \ln \frac{I_{C1}}{I_S} \quad V_T \ln \frac{I_{C2}}{I_S} \quad I_{C2} R_E = 0 \tag{5.14}$$

Al simplificar y agrupar la anterior ecuación y teniendo en cuenta que  $I_{C2}=I_0$  se obtiene la ecuación característica de la fuente Widlar

$V_T \ln \frac{I_{C_1}}{I_0} = I_0 RE$ (5.15)

siendo

$$I_{C1} = \frac{V_{CC} \quad V_{BE}}{R1} \tag{5.16}$$

La resistencia de salida de esta fuente se puede aproximar mediante la expresión

$$Z_{o} = hoe^{\frac{1}{2}} \left( 1 + \frac{{}^{\circ}R_{E}}{h_{ie2} + R_{E}} \right)$$

(5.17)

que como se puede observar su  $Z_0$  es mucho más elevado que el correspondiente a la fuente de corriente basada en espejo de corriente.

La versión de la fuente Widlar basada en transistores MOSFET se representa en la figura 5.6.b y verifica las siguientes ecuaciones

$$\begin{vmatrix}

I_{D1} = \frac{\circ}{2} (V_{GS1} & V_{T})^{2} \\

V_{DD} = I_{ref} R_{1} + V_{GS1} \\

V_{GS1} = V_{GS2} + I_{o} R_{S} \\

I = \frac{\circ}{2} (V_{GS2} & V_{T})^{2}

\end{vmatrix}$$

(5.18)

con una resistencia de salida

$$Z_{o} = r_{d2} + (1 + \alpha)R_{S}$$

(5.19)

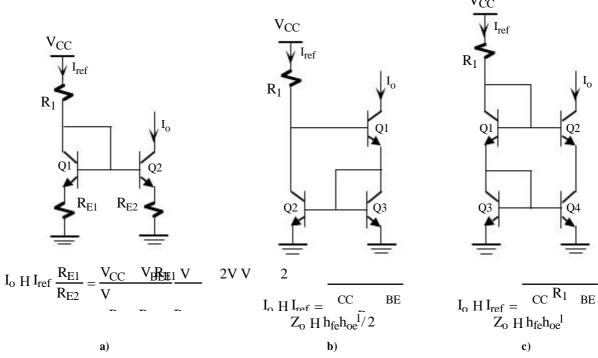

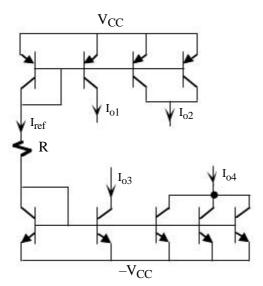

## 5.5.- Otras fuentes de corriente

A partir de la estructura del espejo de corriente y fuentes Widlar se obtienen nuevas fuentes de corriente que mejoran algunas de sus prestaciones. En los circuitos de la figura 5.7 se presentan las más típicas basadas en transistores bipolares. En la fuente de corriente simple con resistencias de emisor de la figura 5.7.a, la relación entre las corrientes de ambos transistores está condicionada por la relación de sus resistencias de emisor. La fuente de corriente Wilson de la figura 5.7.b proporciona corrientes de salida similares al espejo de corriente aumentando enormemente la impedancia de salida. La fuente cascode de la figura 5.7.c presenta una impedancia de salida aún mayor manteniendo niveles de corriente de salida altos.

Las estructuras desarrolladas para transistores bipolares pueden ser adaptadas a transistores MOSFET resultando las fuentes de corriente de la figura 5.8. Están basadas en espejos de corriente y la corriente de salida se especifica a partir de  $I_{ref}$  y la relación geométrica de las puertas de los transistores M1 y M2. La resistencia de salida es idéntica en todas ellas y se puede aproximar por  $Z_oH\mu r_{d2}$ .

Figura 5.7. Fuentes de corriente basadas en transistores bipolares: a) simple con resistencias de emisor. b) Wilson. c) cascode.

Figura 5.8. Fuentes de corriente con MOSFET: a) cascode. b) Wilson. c) Wilson modificada.

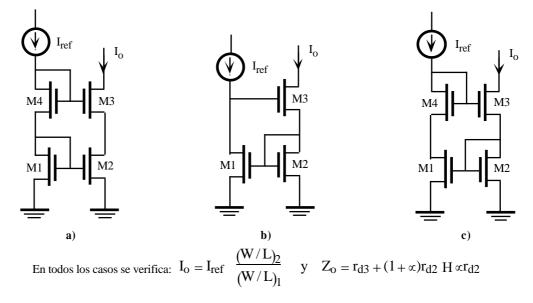

## 5.5.1.- Fuentes de corriente independientes de la tensión de polarización

En muchas aplicaciones es preciso asegurar el funcionamiento del circuito con independencia de las tensiones de alimentación. Las anteriores fuentes de corriente tienen como inconveniente que la intensidad de salida es directamente proporcional a la tensión de alimentación. Por ejemplo, dos espejos de corriente idénticos alimentados con 10V y 30V, el primero tendría corrientes de polarización tres veces inferior al segundo y, por

consiguiente, el segundo disiparía nueve veces más potencia que el primero. Este tipo de fuentes independientes de  $V_{CC}$  pueden se clasificadas en: fuentes que operan con tensiones standard (por ejemplo,  $V_{BE}$  de un transistor) y fuentes basadas en diodos Zener.

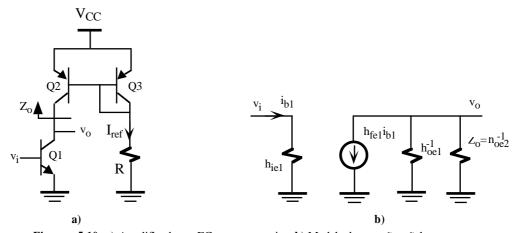

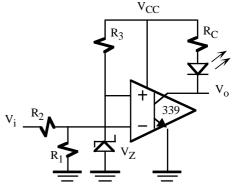

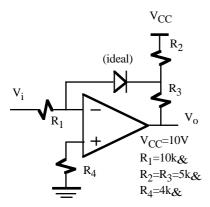

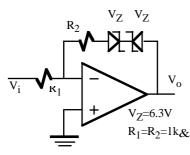

En la figura 5.9.a se muestra una fuente cuya corriente de salida está fijada por la tensión base emisor del transistor Q1 y cuyo valor es

$$I_{o} = \frac{V_{\text{BEI}}}{R_{E}} \tag{5.20}$$

El correcto funcionamiento de este circuito exige que la intensidad de salida  $I_o$  debe ser suficiente elevada para que la caída de tensión en  $R_E$  polarice a Q1 en la región lineal, es decir,  $I_oR_E > V_{BE2@}$ . La independencia de  $I_o$  con la tensión de alimentación no se logra totalmente ya que  $I_{ref}$  depende linealmente de  $V_{CC}$  al verificar  $I_{ref} = (V_{CC} - 2V_{BE})/R_1$ . Una variación en  $I_{ref}$  genera a su vez una variación en  $V_{BE1} = V_T \ln(I_{ref}/I_S)$ , luego  $I_o$  no es totalmente insensible a la tensión de alimentación.

Figura 5.9. Fuentes de corriente independientes de la tensión de alimentación definidas por a)  $V_{BE}$  y b) diodo Zener.

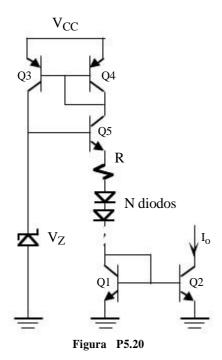

Las fuentes de corriente que utilizan diodos Zener utilizan la tensión zener para obtener tensiones de referencia necesarias para generar una corriente de referencia independiente de la tensión de alimentación. Además, el coeficiente térmico del diodo Zener permite estabilizar estos circuitos frente a las variaciones de la temperatura. Un ejemplo de esta fuente se indica en la figura 5.9.b. La resistencia  $R_1$  polariza al diodo zener y a Q5. Los transistores Q3 y Q4, que actúan como diodos, compensan las tensiones base-emisor de Q5 y Q1. De esta manera, la intensidad que circula por  $R_2$ , que es prácticamente igual a la intensidad de salida  $I_0$  debido al espejo de corriente que forman por Q1 y Q2, vale

$$I_{o} = \frac{V_{\mathcal{L}}}{R_{2}} \tag{5.21}$$

## 5.6.- Fuente de corriente como carga activa

Una fuente de corriente además de actuar como circuito de polarización posee una impedancia interna de alto valor que puede ser utilizada como elemento de carga de amplificadores. Con ello se consigue obtener cargas de un alto valor resistivo con un área de ocupación muy inferior con respecto a las resistencias de difusión de ese mismo valor. En la figura 5.10.a se presenta un ejemplo de un amplificador constituido por el transistor Q1 en configuración E-C que tiene una fuente de corriente simple basada en un espejo de corriente de transistores PNP como carga activa. Al estar el colector de Q1 conectado al de Q2, uno de los problemas de este amplificador consiste en asegurar que ninguno de los transistores entran en saturación. En pequeña señal Q1 "ve" como carga la resistencia de salida  $Z_0(=h_{oe2}^{-1})$  del transistor Q2 que corresponde a la resistencia de salida de un espejo de corriente. La expresión de la ganancia en tensión se obtiene a partir del modelo de pequeña señal de este amplificador (se desprecia  $h_{re}$ ) indicado en la figura 5.10.b y su valor es

$$A_{V} = \frac{h_{fe} \left( h_{oe}^{1} || h_{oe}^{1} \right)}{h_{ie}}$$

(5.22)

Las resistencias de carga en este tipo de circuitos son elevadas lo que se traduce en una alta ganancia de tensión. Por ello, con una o dos etapas amplificadoras de estas características se logran ganancias del orden de 100.000 a 1.000.000, impensable con elementos resistivos.

Figura 5.10. a) Amplificador en EC con carga activa. b) Modelo de pequeña señal.

## **Problemas**

- P5.1 Diseñar un espejo de corriente con transistores NPN y otro con transistores PNP de corrientes de salida 1mA y 0.7mA respectivamente. Dato: h<sub>FE</sub> >> 1.

- P5.2 Calcular el valor de R de la fuente de corriente de la figura 5.1.a para que la intensidad de salida sea de  $100\mu A$ . Datos:  $V_{CC}=15$  V,  $h_{FE}$  >>1. Repetir el problema con  $h_{FE}=10$ .

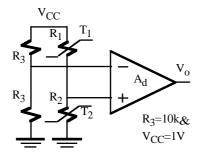

- P5.3 Obtener el valor de las corrientes I<sub>01</sub>, I<sub>02</sub>, I<sub>03</sub> e I<sub>04</sub> del circuito de la figura P5.3. Datos: V<sub>CC</sub>=15V, R=15k&, h<sub>FE</sub> >>1. Proponer una modificación de este circuito que reduzca al mínimo el problema de las corrientes de polarización de base.

Figura P5.3

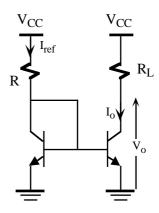

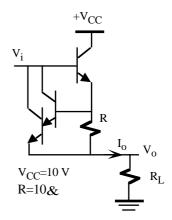

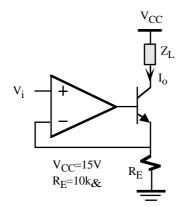

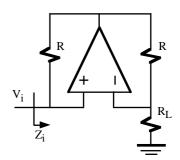

P5.4 Obtener el modelo equivalente Norton de la fuente de corriente de la figura P5.4. para ello, se ha medido experimentalmente que para  $R_L$ =10k& la tensión de salida  $V_o$ =7.5 V, y que para  $R_L$ =50k& se ha obtenido una  $V_o$ =2.5 V. Calcular aproximadamente el rango de valores de  $R_L$  para que opere el circuito correctamente. Dato:  $V_{CC}$ =10 V

Figura P5.4

- P5.5 Determinar el valor de las intensidades de salida de las fuentes de las figuras 5.4.a y 5.4.b en el caso de N=11. Datos: V<sub>CC</sub>=10V, R=23.2k&, β=40.

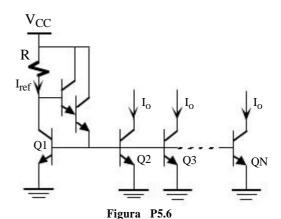

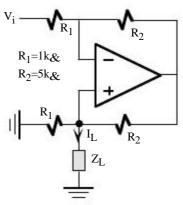

- **P5.6** Obtener la expresión que relaciona  $I_o$  e  $I_{ref}$  en el circuito de la figura P5.6.

- P5.7 Calcular el valor de  $I_o$  de la fuente de corriente de la figura 5.5.a. Datos:  $(W/L)_1 = (W/L)_2 = 10$ ,  $V_T = 1V$ ,  $k = 100 \mu A/V^2$ , R = 16k&,  $V_{DD} = 10V$ .

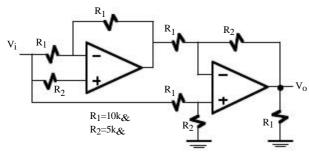

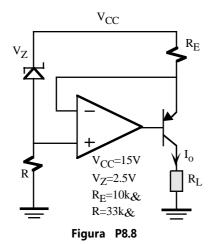

- P5.8 Calcular el valor de I<sub>o</sub> del circuito de la figuraP5.8.

Figura P5.8

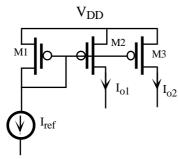

P5.9 Si en el circuito de la figura P5.9  $I_{ref}$ =1mA, determinar el valor de  $I_{o1}$  e  $I_{o2}$ . Datos:  $(W/L)_1$ =1  $(W/L)_2$ =10 y  $(W/L)_3$ =0.1.

Figura P5.9

- P5.10 Determinar el valor de  $R_E$  de la fuente de corriente Widlar de la figura 5.6.a para que proporcione una intensidad de salida de  $10\mu A$ . Datos:  $V_{CC}=30~V, R_1=29.3k$ .

- **P5.11** Si en la anterior fuente, la intensidad que circula por  $R_1$  es de 1mA y  $R_E$ =5k&, calcular el valor de Io.

- P5.12 Diseñar una fuente de corriente Wilson con transistores PNP con una intensidad de salida de 0.8mA.

- P5.13 Calcular el valor de  $I_o$  de la fuente de corriente de la figura 5.6.b. Datos:  $(W/L)_1=(W/L)_2=10$ ,  $V_T=1V$ ,  $k=100\mu A/V^2$ ,  $R_1=6k8$ &,  $R_S=330$ &,  $V_{DD}=10V$ .

- P5.14 Calcular la  $I_o$  y  $Z_o$  de la fuente de corriente cascode de la figura 5.7.c si los transistores tienen unas características eléctricas similares al BC547B. Datos:  $V_{CC}$ =10 V, R=8.6k&.

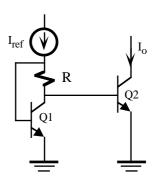

P5.15 Obtener el valor de I<sub>o</sub> de la fuente de bajo nivel de corriente de la figura P5.15. Despreciar las intensidades de base. I<sub>ref</sub>=0.1mA, R=1k&.

Figura P5.15

P5.16 En la figura P5.16 se muestra una fuente de corriente cascode basada en transistores NMOS, todos ellos con la misma relación geométrica (W/L)=10. Calcular el valor de la corriente de salida. Datos: V<sub>T</sub>=1V, k=33μA/V<sup>2</sup>, R=13.5k&, V<sub>DD</sub>=10V.

Figura P5.16

- P5.17 Determinar el valor de  $I_o$  de la fuente de corriente de la figura 5.9.a. Despreciar las intensidades de base. Datos:  $V_{CC}$ =15V,  $R_1$ =10k& y  $R_E$ =1k&.

- P5.18 Repetir el problema anterior considerando que los transistores tienen una  $I_S=10^{-16}$  A. Despreciar las intensidades de base.

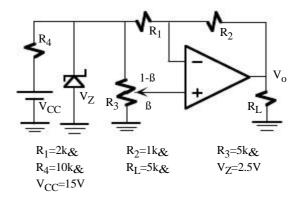

- P5.19 Determinar el valor de R<sub>2</sub> para que la

intensidad de salida del circuito de la figura 5.9.b sea de 1mA. Despreciar las intensidades de base. Datos:  $V_{CC}$ =15 V,  $V_{Z}$ =4 V y  $R_{1}$ =10k&.

P5.20 Calcular el valor de  $I_o$  de la fuente de corriente independiente de la tensión de alimentación mostrada en la figura P5.20. Despreciar las intensidades de base. Datos:  $V_{CC}$ = 10 V, R=10k&,  $V_{Z}$ =4 V y N=2.

P5.21 En la fuente de corriente del problema P5.20 determinar el número máximo N de diodos que puede tener ese circuito.

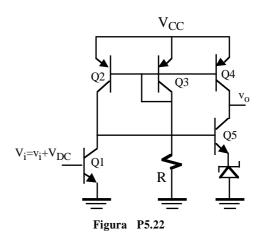

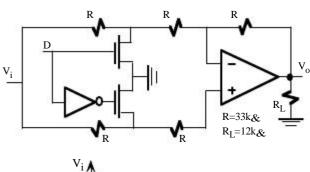

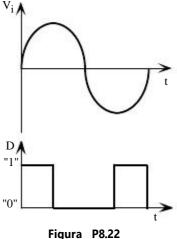

- P5.22 Para el amplificador multietapa con carga activa de la figura 5.22, se pide:

- a) Calcular las corrientes de colector de todos los transistores. Determinar el valor de la tensión en continua ( $V_{DC}$ ) a la entrada de Q1 para su correcta polarización.

- b) Obtener el modelo de tensión equivalente del amplificador.

- c) Explicar la finalidad del diodo zener. Despreciar las corrientes de base. Datos: NPN:  $I_S$ =0.5  $10^{-15}$ ,  $h_{oe}$ =1/100k&,  $h_{ie}$ =5k&,  $h_{fe}$ =200; PNP:  $I_S$ =0.7  $10^{-15}$ ,  $h_{oe}$ =1/80k&,  $h_{ie}$ =6k&,  $h_{fe}$ =150, R=10k&,  $V_{CC}$ =10  $V_{SC}$ =4  $V_{CC}$ =4  $V_{CC}$ =10

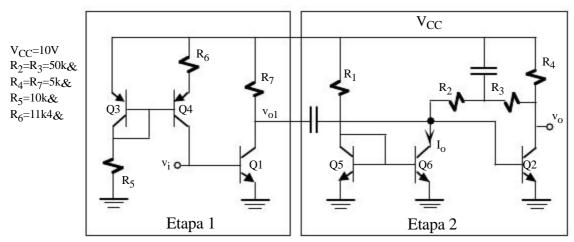

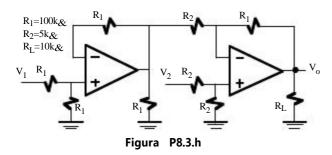

P5.23 El circuito de la figura P5.23 es una amplificador constituido por dos etapas básicas que utiliza fuentes de intensidad en su polarización. Se pide:

Figura P5.23

## a) Para la etapa 1:

- a.1) Calcular la I<sub>C</sub> del transistor Q1.

- a.2) Determinar el valor de R<sub>5</sub> que haga entrar al transistor Q1 en saturación.

- a.3) Modelo equivalente en intensidad de este etapa.

## b) Para la etapa 2:

- b.1) Calcular el valor de  $\,R_1\,$  para que la  $\,I_B\,$  de Q2 sea de  $\,10\mu A.\,$

- b.2) Calcular el valor de  $I_o$  que haga entrar en corte al transistor Q2.

- b.3) ¿Existe algún valor de I<sub>o</sub> que haga entrar al transistor Q2 en saturación?. ¿Por qué?

- b.4) Modelo equivalente en tensión de esta etapa. Dato:  $R_1$ =400k&.

- c) Obtener el modelo equivalente en tensión del amplificador completo a partir de los modelos calculados en a.3 y b.4.

Para todos los transistores:

NPN:  $h_{FE}=100$ ,  $V_{BE}=0.7$  V,  $V_{CE(sat)}=0.2$  V,

$h_{fe}=120, h_{ie}=5k$ ,  $h_{oe}=h_{re}=0$ .

PNP:  $h_{FE}=80$ ,  $V_{EB}=0.7$  V,  $V_{EC(sat)}=0.2$  V,

$h_{fe}=70, h_{ie}=4k\&, h_{oe}=h_{re}=0.$

# TEMA 6

## **Amplificador diferencial**

## 6.1.- Introducción

El amplificador diferencial es un circuito que constituye parte fundamental de muchos amplificadores y comparadores y es la etapa clave de la familia lógica ECL. En este tema se describen y analizan diferentes tipos de amplificadores diferenciales basados en dispositivos bipolares y FET. Se abordan técnicas de polarización y análisis de pequeña señal introduciendo los conceptos en modo diferencial y modo común que permiten simplificar el análisis de estos amplificadores. Por último, se presentan y estudian amplificadores diferenciales integrados complejos que resultan muy útiles como introducción a los amplificadores operacionales.

## 6.2.- Análisis de un amplificador diferencial básico bipolar

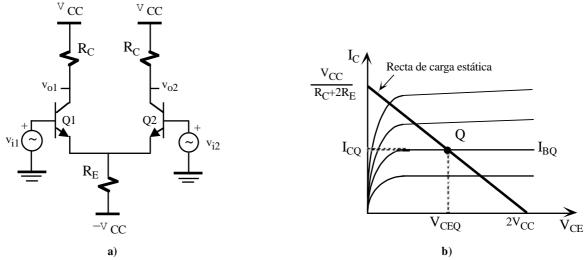

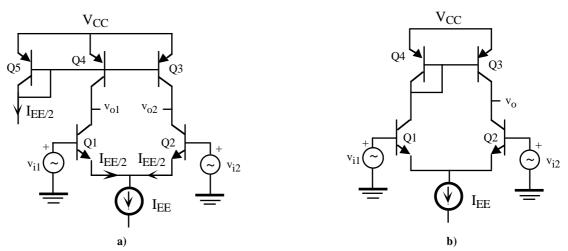

El amplificador diferencial constituye la etapa de entrada más típica de la mayoría de los amplificadores operaciones y comparadores, siendo además el elemento básico de las puertas digitales de la familia lógica ECL. En la figura 6.1.a aparece la estructura básica de este amplificador. Uno de sus aspectos más importantes es su simetría que le confiere unas características muy especiales de análisis y diseño. Por ello, los transistores Q1 y Q2 deben ser idénticos, aspecto que únicamente se logra cuando el circuito está fabricado en un chip. Realizar este amplificador con componentes discretos pierde sus principales propiedades al romperse esa simetría. A continuación se realiza un análisis de este amplificador, primero en continua y luego en alterna donde se introducen los conceptos de configuración en modo común y modo diferencial.

Figura 6.1. a) Amplificador diferencial básico y b) recta de carga estática.

#### 6.2.1.- Análisis en continua

En el caso de que  $v_{i1}$  y  $v_{i2}$  sean componentes de pequeña señal, y suponiendo que  $h_{FE}>>1$ , entonces se puede extraer del circuito de la figura 6.1 a la siguiente relación

$$0 \text{ H V}_{BE} + (I_{E1} + I_{E2})R_E \quad V_{CC}$$

(6.1)

La simetría del circuito y el hecho de que Q1 y Q2 son transistores idénticos hace que  $I_{E1}=I_{E2}=I_{E}$  de forma que

$$I_{E} H I_{C} = \frac{V c c V_{BE}}{2R_{E}}$$

(6.2)

La ecuación de recta de carga estática se obtiene aplicando KVL a la malla colector-emisor de los transistores:

$$2V_{CC} H V_{CE} + I_{C}(R_{C} + 2R_{E})$$

(6.3)

Esta recta se encuentra dibujada en la figura 6.1.b. La situación del punto de trabajo define los límites de variación de señal de entrada y el rango de funcionamiento lineal permisible. La máxima amplitud de salida se consigue cuando  $V_{CEO}=V_{CC}$ .

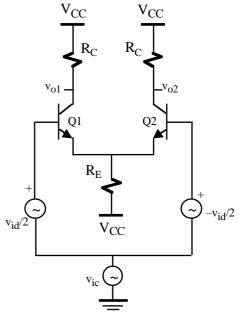

#### 6.2.2.- Análisis de las configuraciones en modo común y diferencial

La simetría del amplificador diferencial permite simplificar su análisis convirtiendo las tensiones de entrada en tensiones de entrada de modo común y modo diferencial. Además, estos conceptos están en consonancia con las aplicaciones típicas del amplificador operacional que se suele utilizar para amplificar la diferencia entre las dos señales de entrada. La tensión de entrada en modo diferencial ( $v_{id}$ ) y modo común ( $v_{ic}$ ) se definen como

$$\begin{cases} v_{id} = v_{i1} & v_{i2} \\ v_{ic} = \frac{v_{i1} + v_{i2}}{2} \end{cases} \quad o \quad \begin{cases} v_{i1} = v_{id} / 2 + v_{ic} \\ v_{i2} = \pm v_{id} / 2 + v_{ic} \end{cases}$$

$$(6.4)$$

A su vez, estas tensiones  $v_{id}$  y  $v_{ic}$  dan lugar a dos tensiones de salida, en modo diferencial ( $v_{od}$ ) y modo común ( $v_{oc}$ ), definidas de una manera similar como

$$y_{od} = v_{o1} \quad v_{o2}$$

$$\int_{V_{oc}} v_{o1} = \frac{v_{o1} + v_{o2}}{2}$$

o

$$y_{o1} = v_{od} / 2 + v_{oc}$$

$$\int_{V_{o2}} v_{o2} = \pm v_{od} / 2 + v_{oc}$$

(6.5)

**Figura 6.2**. Amplificador diferencial con tensiones en modo diferencial y modo común.

Con la definición de las tensiones en modo diferencial y modo común, el amplificador diferencial tiene dos ganancias, una en modo diferencial  $(A_d)$  y otra en modo común  $(A_c)$  definidas como

$$A_{d} = \frac{v_{oa}}{v_{id}} \quad y \quad A_{c} = \frac{v_{oc}}{v_{ic}}$$

(6.6)

La aplicación de los estos conceptos permite transformar el circuito de la figura 6.1.a en el de la figura 6.2. Este nuevo circuito presenta unas propiedades de simetría que facilita su análisis mediante la aplicación del principio de superposición a las entradas en modo diferencial y común independientemente.

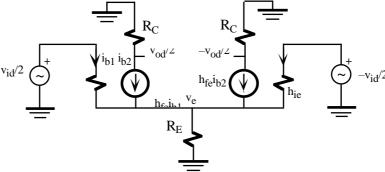

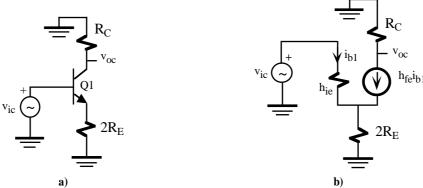

#### · Ganancia en modo diferencial

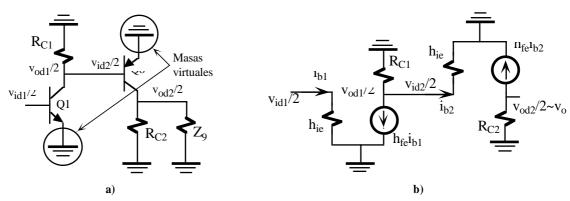

En la figura 6.3 se muestra el circuito equivalente simplificado del amplificador diferencial cuando únicamente se considera modo diferencial a la entrada. El análisis del circuito establece las siguientes ecuaciones

$$y_{id}/2 = i_{b1}h_{ie} \quad i_{b2}h_{ie} \quad v_{id}/2 \otimes v_{id} = (i_{b1} \quad i_{b2})h_{ie}$$

$$|v_{e}| = (i_{b1} + i_{b2})(1 + h_{fe})R_{E}$$

$$|v_{id}/2 = i_{b1}h_{ie} + v_{e}$$

$$R_{C}$$

Figura 6.3. Circuito de pequeña señal simplificado del amplificador diferencial en modo diferencial (h<sub>oe</sub>=h<sub>re</sub>=0).

Resolviendo las ecuaciones de 6.7 se llega fácilmente a la siguiente relación

$$(i_{b1} + i_{b2})(h_{ie}/2 + (1 + h_{fe})R_E) = 0$$

(6.8)

siendo la única solución posible

$$\begin{bmatrix}

i_{b1} = i_{b2}

\end{bmatrix}$$

(6.9)

resultando que

$$v_e = 0 ag{6.10}$$

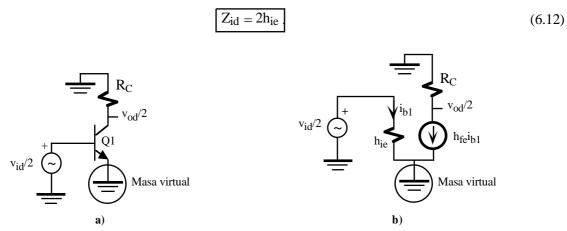

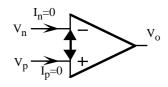

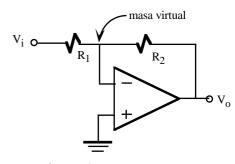

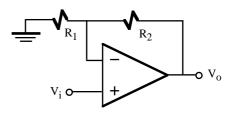

La ecuación (6.10) indica que la tensión de pequeña señal en el emisor de los transistores es nula, es decir, que ese nudo se comporta como un nudo de <u>masa virtual</u>; no hay que confundirla con la masa real del circuito. Por consiguiente, analizar el circuito de la figura 6.3 es equivalente a analizar los circuitos equivalentes del amplificador diferencial en modo diferencial mostrados en las figuras 6.4.a y 6.4.b. La ganancia en tensión en modo diferencial de este amplificador es

$$A_d = \frac{v_{od}/2}{v_{id/2}} = \frac{hreRc}{h_{ie}}$$

(6.11)

La impedancia de entrada del circuito de la figura 6.4 es  $Z_i$ = $h_{ie}$ . Por consiguiente, la impedancia de entrada vista a través de los dos terminales de entrada diferencial es

**Figura 6.4.** Circuitos equivalente del amplificador diferencial en modo diferencial **a**) en alterna, **b**) en pequeña señal  $(h_{Oe} = h_{re} = 0)$ .

#### · Ganancia en modo común

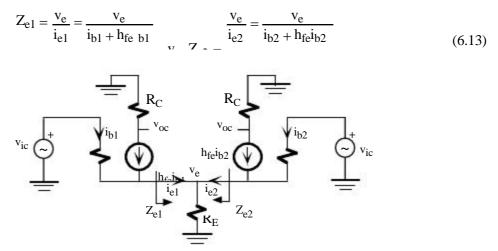

En la figura 6.5 aparece el circuito equivalente del amplificador diferencial cuando únicamente se considera modo común a la entrada. Para obtener un circuito más simplificado se va a determinar en primer lugar las impedancias equivalentes  $Z_{e1}$  y  $Z_{e2}$  vista a través de los emisores de los transistores Q1 y Q2. Estas impedancias se definen como

**Figura 6.5**. Amplificador diferencial en modo común. ( $h_{oe}=h_{re}=0$ ).

Analizando el circuito de la figura 6.5 se obtiene la siguiente ecuación

$$v_{ic} = i_{b1}h_{ie} \quad i_{b2}h_{ie} + v_{ic}$$

(6.14)

que permite demostrar que

$$i_{b1} = i_{b2}$$

(6.15)

Por otra parte, la tensión v<sub>e</sub> se puede expresar como

$$v_e = (i_{b1} + h_{fe}i_{b1} + i_{b2} + h_{fe}i_{b2})R_E$$

(6.16)

**Figura 6.6.** Circuitos equivalente del amplificador diferencial en modo común  $\bf a$ ) en alterna,  $\bf b$ ) en pequeña señal ( $h_{oe}$ = $h_{re}$ =0).

y utilizando las ecuaciones 6.13, 6.14 y 6.15 fácilmente se demuestra que

$$Z_{e1} = Z_{e2} = 2R_E$$

(6.17)

Luego, los emisores de Q1 y Q2 "ven" una resistencia equivalente expresada en 6.17 de forma que el circuito de la figura 6.5 se transforma en los circuitos equivalentes más sencillos mostrados en la figuras 6.6.a y 6.6.b. Fácilmente se demuestra que la ganancia en modo común es

$$A_{c} = \frac{v_{o1}}{v_{ic}} = \frac{v_{oc}}{v_{ic}} = \frac{h_{fe}R_{C}}{h_{ie} + 2R_{E}(1 + h_{fe})}$$

(6.18)

#### • Relación de rechazo en modo común

Un amplificador diferencial ideal tiene una tensión de salida proporcional a  $v_{id}$  y no depende de la componente en modo común ( $A_c$ =0). En la práctica no sucede así y para medir esa desviación se introduce el concepto de relación de rechazo en modo común RRMC; en inglés *common-mode rejection ratio* o CMRR. Se define la RRMC como la relación entre la ganancia en modo diferencial y modo común

$$RRMC = \frac{A_d}{A_c} \tag{6.19}$$

que a veces se expresa en decibelios como

$$RRMC(dB) = 20 \log_{10} \left| \frac{A u}{A_c} \right|$$

(6.20)

## 6.3.- Amplificador diferencial bipolar con fuente de corriente

En la etapa diferencial anterior una RRMC muy elevada exige una  $R_E$  grande; en el caso ideal RRMC $\square$  si

$R_E$ . Sin embargo, la polarización del transistor es fuertemente dependiente del valor de esta resistencia. Una alternativa que se utiliza en la práctica consiste en sustituir la resistencia  $R_E$  por una fuente de corriente. De esta manera, la polarización del circuito puede realizarse con facilidad y la RRMC es muy elevada ya que una fuente de corriente presenta una impedancia interna muy alta.

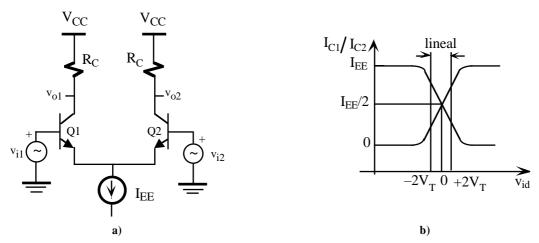

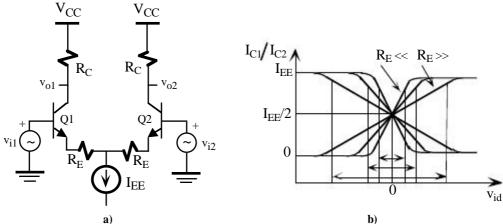

Figura 6.7. a) Amplificador diferencial polarizado con fuente de corriente. b) Característica de transferencia del circuito.

En la figura 6.7.a se muestra un amplificador diferencial polarizado con una fuente de corriente de valor  $I_{\text{EE}}$ . Esta corriente se reparte simétricamente en ambos transistores resultando que en continua

$$I_{C1} H I_{C2} H \frac{I_{EE}}{2}$$

(6.21)

Cuando se aplica una tensión de entrada diferencial, la suma de corriente en ambos transistores se mantiene constante a I<sub>EE</sub>, es decir,

$$I_{C1} + I_{C2} = I_{EE} (6.22)$$

Esto significa que un incremento de corriente en un transistor origina una disminución de corriente en la misma proporción en el otro transistor. La gráfica de la figura 6.7.b presenta la característica de transferencia del amplificador cuando se aplica una tensión en modo diferencial. Este circuito opera con tensiones máximas de entrada en modo diferencial bajas; del orden de  $100 \text{mV} \sim 4 \text{V}_T$ . Superado este valor uno de los transistores se corta y por el otro circula toda la corriente  $I_{EE}$ . Las características de transferencia son lineales en una pequeña región de operación ( $\pm 2 \text{V}_T$ ). Una modificación de este amplificador para que trabaje con tensiones en modo diferencial mayores consiste en añadir una resistencia de emisor tal como se describe en la figura 6.8.a. Este circuito mantiene la simetría de un amplificador diferencial aumentando el rango de tensiones de entrada. Este efecto se puede observar claramente en la figura 6.8.b en donde la característica de transferencia tiene un rango de entrada lineal mayor según aumenta  $R_E$ . El inconveniente es que la ganancia en modo diferencial disminuye. Para este circuito, se puede demostrar que si  $h_{re} = h_{oe} = 0$ , la ganancia en modo diferencial vale

$$A_{d} = \pm \frac{h_{fe}R_{C}}{h_{ie} + (1 + h_{fe})R_{E}}$$

(6.23)

Valores razonables de  $R_{\rm E}$  deben estar comprendidos entre 50 a 100& ya que con valores grandes la  $A_{\rm d}$  se reduce excesivamente.

**Figura 6.8.** a) Amplificador diferencial con resistencia de emisor. b) Característica de transferencia del circuito para diferentes valores de resistencia de emisor.

### 6.3.1.- Amplificador diferencial con carga activa

Las fuentes de corriente pueden ser utilizadas como carga activa en un amplificador diferencial. El espejo de corriente es el circuito que mejor se adapta al tener una resistencia interna no demasiado elevada la cual elimina problemas de polarización y mantiene una ganancia muy alta. La figura 6.9.a muestra la estructura de un amplificador diferencial que tiene una carga activa constituida por el espejo de corriente formado por los transistores PNP Q3, Q4 y Q5. Por necesidades de polarización la intensidad de referencia de este espejo tiene que ser la mitad de  $I_{EE}$  ya que las intensidades de colector de Q1 y Q4, y Q2 y Q3 deben ser idénticas. Fácilmente se puede comprobar aplicando las propiedades de simetría del amplificador diferencial que la ganancia en modo diferencial es

$$A_{d} = h_{fe} \frac{h_{oep}^{1} || h_{oen}}{h_{ie}}$$

(6.24)

donde h<sub>oep</sub> y h<sub>oen</sub> es la resistencia de salida de un transistor PNP y NPN respectivamente.

Figura 6.9. Amplificador diferencial con a) carga activa y b) carga activa modificada.

En la figura 6.9.b se presenta un amplificador diferencial con una carga activa constituida por un espejo de corriente (Q3,Q4) que necesita menos dispositivos que el caso anterior. Tiene una única salida que proporciona

una conversión de entrada diferencial-salida simple (differential to single-ended conversion) y, aunque en principio se rompe la simetría del amplificador diferencial, este circuito tiene una ganancia en modo diferencial que se aproxima al valor expresado en la ecuación 6.24.

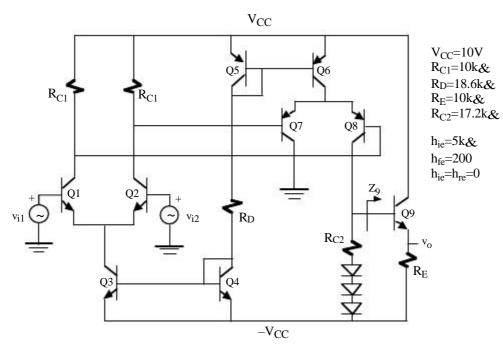

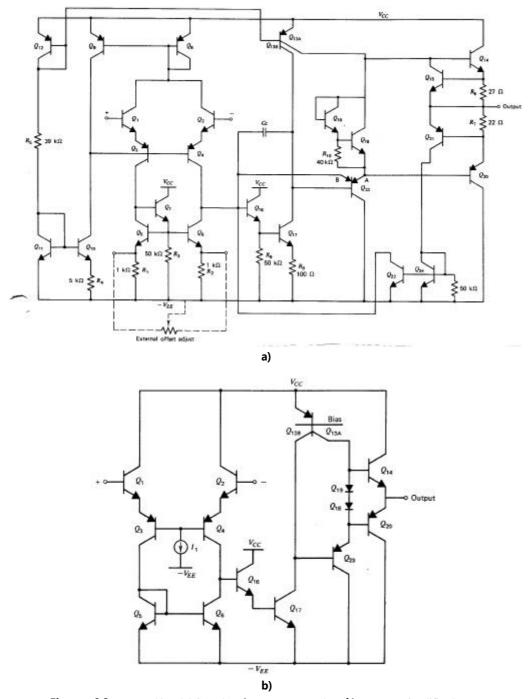

#### 6.3.2.- Ejemplo de un amplificador diferencial bipolar complejo

En este apartado se va a realizar una análisis simplificado un amplificador diferencial completo de la figura 6.10 constituido por varias etapas amplificadoras conectadas en cascada. Básicamente, es un amplificador operacional formado por una etapa diferencial de entrada (Q1,Q2), otra etapa diferencial intermedia (Q7,Q8) y la etapa de salida en configuración de seguidor de emisor (Q9).

Figura 6.10. Amplificador diferencial completo.

• <u>Análisis DC</u>. El análisis en continua de este amplificador se realiza suponiendo nulas las entradas  $v_{i1}$  y  $v_{i2}$  y despreciando las corrientes de base.. En la polarización de las etapas diferenciales se utiliza dos espejos de corriente, uno basado en transistores NPN (Q3,Q4) y otro en PNP (Q5,Q6), cuya corriente de referencia se fija a través de  $R_D$ . Si se desprecia las corrientes de base de los transistores se verifica que

$$\frac{2V_{CC} \quad BE}{R_{D2}V} = 1mA \tag{6.25}$$

Por consiguiente, aplicando el principio de simetría a ambos amplificadores diferenciales

$$I_{C1} H I_{C2} H I_{C7} H I_{C8} = \frac{I_{EE}}{2} = 0.5 \text{mA}$$

(6.26)

Luego, la tensión de salida

$$v_0 H I_{C8} R_{C2} + 3 V_D V_{BE9} V_{CC} = 0V$$

(6.27)

es nula en ausencia de señal.

Figura 6.11. a) Aplicación del principio de simetría al circuito de la figura 6.10; b) Modelo equivalente de pequeña señal.

• Análisis de pequeña señal. Al despreciar el parámetro  $h_{oe}$  los espejos de corriente son ideales resultando que la ganancia en modo común es nula. Ello permite aplicar los principios de simetría del amplificador diferencial en modo diferencial, reduciendo el análisis de este amplificador al circuito mostrado en la figura 6.11.a. La tensión de salida  $v_o$  es prácticamente la tensión del colector de Q8 al ser la ganancia en tensión de la etapa de salida prácticamente 1 (se trata de una seguidor de emisor). Además, Q8 tiene como carga la resistencia  $R_{C2}$  y la impedancia de entrada de Q9 que en la figura 6.11.a. se representa por  $Z_9$ . El valor de  $Z_9$  es

$$Z_9 = h_{ie} + (1 + h_{fe}R_E) H 2M_{\&}$$

(6.28)

Por consiguiente, se puede hacer la siguiente aproximación  $R_{C2}||Z_9ER_{C2}$ . La ganancia del amplificador de la figura 6.11.a se puede obtener resolviendo el circuito equivalente de la figura 6.11.b. De esta forma,

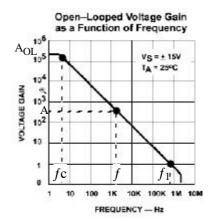

$$A_{d} = \frac{v_{o}}{v_{id1}/2} = \frac{v_{od2/2}}{v_{id1}/2} = \frac{v_{od1}/2}{v_{id1}/2} \frac{v_{od2}/2}{v_{od1}/2} = A_{d1}A_{d2} =$$

$$= \left| \frac{h_{fe}(R_{C1} || h_{ie})|}{h_{ie} || h_{ie}} \right| \left| \frac{h_{fe}R_{C2}}{h_{ie} || h_{ie}} \right| || H 92 \oplus 10^{3}$$

(6.29)

Luego, la ganancia del amplificador completo

$$A_{OL} = \frac{1}{V_{id}} = \frac{1}{4} \frac{1}{V_{id}V_{o}/2} = \frac{1}{A_{d}} H 46 \theta 10^{3}$$

(6.30)

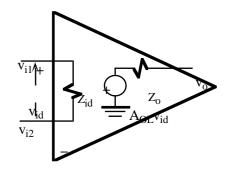

La impedancia de entrada en modo diferencial es  $Z_{id}\!\!=\!\!2h_{ie}\!\!=\!\!10k$  , y la impedancia de salida vale

$$Z_{o} = R_{E} \parallel \frac{\overline{R_{C2} + h_{ie}}}{1 + h_{fe}} = \overline{R_{C2} + h_{ie}} = 110\&$$

(6.31)

En la figura 6.12 se muestra el modelo equivalente del amplificador completo.

**Figura 6.12**. Modelo equivalente simplificado del amplificador de la figura 6.10.

## 6.4.- Amplificadores diferenciales FET

La impedancia de entrada de un amplificador diferencial puede ser muy alta si se utiliza transistores FET. La

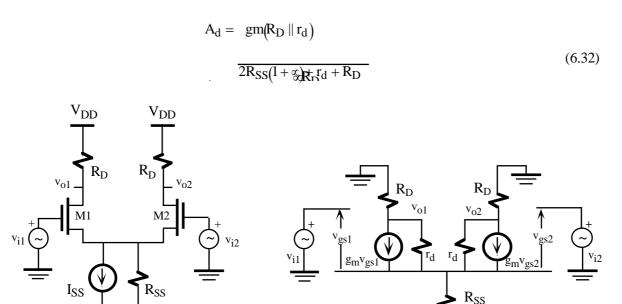

figura 6.13.a presenta un amplificador diferencial básico basado en los transistores NMOS, M1 y M2, cuya polarización se realiza a través de una fuente de corriente de valor I<sub>SS</sub> con una resistencia interna R<sub>SS</sub> y la figura 6.13.b muestra el circuito equivalente de pequeña señal. Al presentar este amplificador las mismas características de simetría descritas en el amplificador diferencial bipolar se puede utilizar la conversión a señal modo diferencial y modo común. Por similitud, en modo diferencial el terminal fuente de estos transistores se comporta como un nudo de masa virtual y en modo común la resistencia R<sub>SS</sub> se descompone en dos en paralelo. Aplicando estos principios de simetría es sencillo comprobar que la ganancia en modo diferencial y común vale

Figura 6.13.a) Amplificador diferencial simple de transistores NMOS. b) Circuito equivalente de pequeña señal.

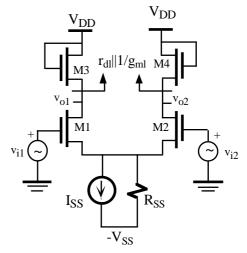

La ganancia de este amplificador puede mejorarse utilizando cargas activas. En las figura 6.14 aparece un amplificador diferencial NMOS con carga activa formado por los transistores M3 y M4. M3 y M4 tienen la puerta y el drenador cortocircuitado de forma que en pequeña señal pueden ser sustituidos por un elemento resistivo de valor  $r_{dl} \| 1/g_{ml}$  (subíndice l de *load*). Las expresiones de la  $A_d$  y  $A_c$  son similares a las descritas en la

ecuación 6.32 sustituyendo la  $R_{D}$  por la carga equivalente  $r_{\text{dl}} \| 1/g_{\text{ml}}.$

-V<sub>SS</sub> a)

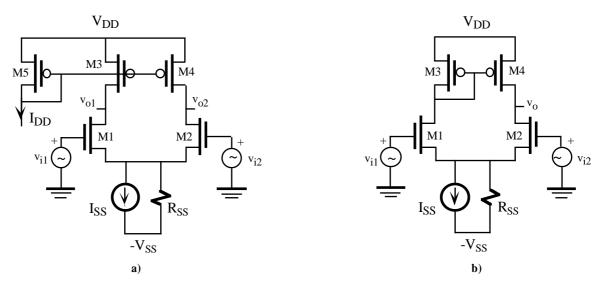

La tecnología CMOS permite realizar también amplificadores diferenciales con carga activa. El amplificador de la figura 6.15.a utiliza un espejo de corriente de transistores PMOS como carga activa y el de la figura 6.15.b otro espejo de corriente autopolarizado con salida simple que realiza una conversión salida simple-entrada diferencial. Em ambos casos se puede demostrar que, en primera aproximación, las ganancias en modo diferencial y común valen

$$A_{d} = \pm g_{mi}(r_{dl} || r_{di})$$

$y$   $A_{c} = \frac{1}{2g_{mi}R_{SS} || 1 + || dt ||}$  (6.33)

**Figura 6.14.** Amplificador diferencial NMOS con carga activa.

siendo el subíndice l relacionado con M3 y M4 y el subíndice i con M1 y M2.

Figura 6.15. Amplificador diferencial CMOS con a) espejo de corriente y b) autopolarizado.

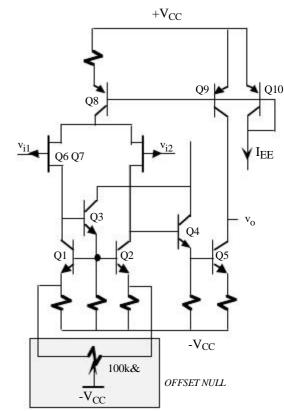

Los transistores JFET al tener una tecnología compatible con los BJT pueden ser simultáneamente en un circuito integrado. Con ello, se combina las características de ambos dispositivos como son su alta impedancia de entrada (JFET) y linealidad y altas prestaciones (BJT). En la figura 6.16 se muestra un ejemplo práctico correspondiente a la etapa de entrada del amplificador operacional TL080 de Texas Instruments que utiliza PJFET como transistores de entrada de la etapa diferencial y transistores bipolares para polarización y amplificación. La etapa de entrada diferencial está constituida por Q6 y Q7 cuya carga activa lo forma la fuente de corriente Q1 y Q2; las corrientes de entrada son del orden de pA. Q4 actúa como amplificador en configuración seguidor de emisor con objeto de introducir una carga de muy alto valor a Q7 y servir de etapa de interfase con la siguiente etapa amplificadora basada en Q5. Q3 introduce una carga similar a Q4 para mantener la simetría de la etapa diferencial. Q8, Q9 y Q10 son fuentes de corriente (Widlar y espejo de corriente respectivamente) para polarización del circuito. Como es frecuente en los amplificadores operacionales, factores de disimetría en la etapa diferencial hace que en ausencia de señal de entrada

**Figura 6.16**. Etapa de entrada del TLO80 basada en JFET con corrección de *offset*.

la salida no sea nula, en contra de lo que debe suceder en teoría (*offset null*). Para corregir este efecto, algunos amplificadores tienen salidas al exterior que mediante un potenciómetro variable se corrige el desequilibrio de la etapa diferencial y se anula este efecto. En la figura se indica la situación y valor típico del potenciómetro.

## **Problemas**

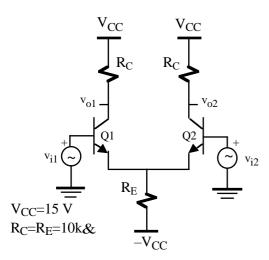

- P6.1 Para el amplificador diferencial de la figura P6.1, se pide:

- a) La tensión  $v_{o1}$  y  $v_{o2}$  en DC.

- b) Ganancia en modo diferencial y común.

- c) Si  $v_{i1}$ =1.02V senwt y  $v_{i2}$ =1.025V senwt, determinar la  $v_{od}$ ,  $v_{oc}$ ,  $v_{o1}$  y  $v_{o2}$ .

Datos:  $h_{FE}=100$ ,  $h_{fe}=100$ ,  $h_{ie}=3333$ &,  $h_{re}=h_{oe}=0$ .

Figura P6.1

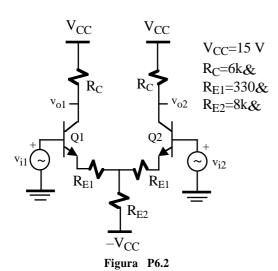

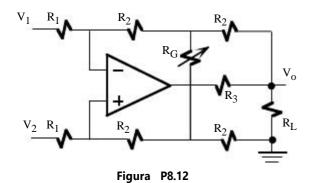

P6.2 Repetir el problema P6.1 con el circuito de la figura P6.2.

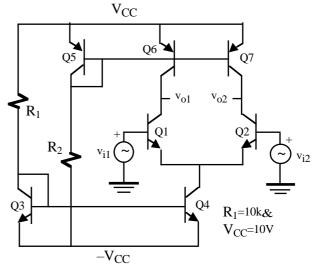

- P6.3 En la figura P6.3 se muestra un amplificador diferencial con carga activa (transistores Q6 y Q7). ¿Qué ventajas e incovenientes presenta una carga activa frente a una carga resistiva?. Para este circuito, se pide:

- a) el valor adecuado de R<sub>2</sub> para que el circuito se encuentre polarizado correctamente. Despreciar las corrientes de base.

- b)  $A_d y A_c$ .

Datos: NPN:  $h_{ie}$ =5k&,  $h_{fe}$ =100,  $h_{oe}$ =1/50k&,  $h_{re}$ ~0. PNP:  $h_{ie}$ =6k&,  $h_{fe}$ =60,  $h_{oe}$ =1/50k&,  $h_{re}$ ~0.

Figura P6.3

P6.4 Calcular la tensión  $v_{o1}$  y  $v_{o2}$  en continua y la  $A_d$  del amplificador diferencial basado en un par Darlington de la figura P6.4. Datos:  $h_{FE}$ =90,  $h_{ie}$ =5k&,  $h_{fe}$ =100,  $h_{re}$ = $h_{oe}$ =0.

Figura P6.4

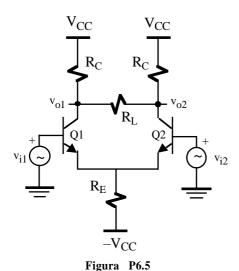

P6.5 Comprobar que aplicando el principio de simetría el amplificador diferencial de la figura P6.5 verifica las siguientes expresiones. Nota:  $h_{re}=h_{oe}=0$ .

$$A_d = \begin{array}{ccc} \frac{ \text{in} \left\{ R \sim \cdot \cdot \frac{R_L}{2} \right\}_j}{h_{ie}} & y & A_c = & \frac{h_{fe} \kappa_C}{h_{ie} + \left(l + h_{fe}\right) 2 R_E} \end{array}$$

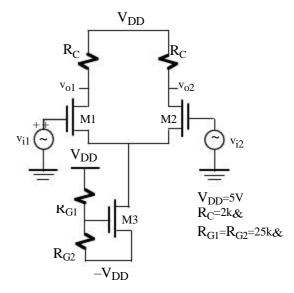

$\begin{array}{llll} \textbf{P6.6} & \textbf{Calcular la } I_D \ \ \text{de los transistores NMOS del} \\ & \text{amplificador diferencial de la figura P6.6.} \\ & \textbf{Determinar la } A_d \ \ y \ \ \text{la tensión de salida } v_{o1} \\ & \textbf{cuando } v_{i1} = 2V + 0.1V \ \text{senwt y } v_{i2} = 2V. \end{array}$

Datos:  $k=33\mu A/V^2, V_T=1V, W_1=W_2=10\mu m, W_3=20\mu m, L_1=L_2=L_3=4\mu m.$

Figura P6.6

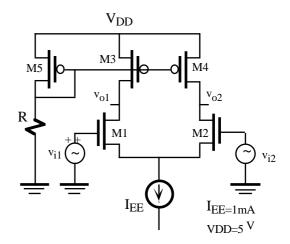

P6.7 Determinar el valor de la resistencia R para que que el circuito de la figura P6.7 esté polarizado correctamente. Calcular el valor de la  $A_d$ .

Datos:  $W_1 = W_2 = 15 \mu m$ ,  $W_3 = W_4 = W_5 = 30 \mu m$ ,  $L_1 = L_2 = L_3 = L_4 = L_5 = 4 \mu m$

NMOS:  $k=66\mu A/V^2, V_T=1V$ ,  $gm_1=gm_2=1m\&^{-1}, r_{d1}=r_{d2}=100k\&$ ;

PMOS:  $k=33\mu A/V^2$ ,  $V_T=-1V$ ,  $gm_3=gm_4=gm_5=0.5m\&^{-1}$ ,  $r_{d3}=r_{d4}=r_{d5}=150k\&$ .

Figura P6.7

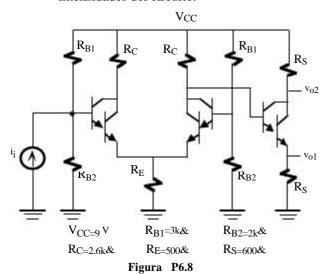

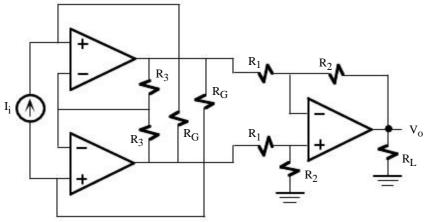

P6.8 Calcular la tensión  $v_{o1}$  y  $v_{o2}$  en continua y la relación  $A_1 = v_{o1}/i_i$  y  $A_2 = v_{o2}/i_i$  del amplificador de la figura P6.8. Datos:  $h_{fe} = 100$ ,  $h_{ie} = 2k$ . Nota: Despreciar las intensidades de base frente al resto de las

intensidades del circuito.

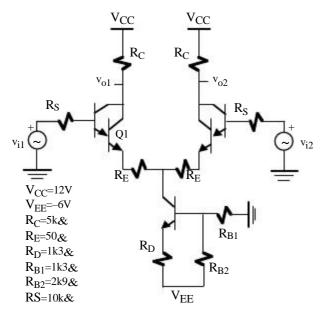

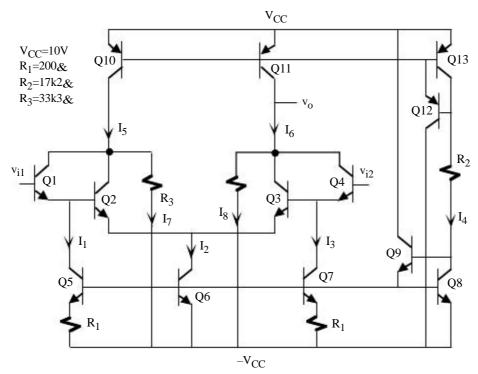

- P6.9 El circuito de la figura P6.9 es un amplificador diferencial típico de un amplificador operacional. Para este circuito se pide:

- a) Calcular las intensidades  $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_4$ ,  $I_5$  e  $I_6$  y el valor de  $v_0$  en continua. Utilizar los principios de simetría de los amplificadores diferenciales. Despreciar la  $I_B$  frente a  $I_C$  ( $I_B << I_C$ ).

- b) Calcular la ganancia en modo diferencial.

- c) Si  $v_{i1}=10$ mV senwt y  $v_{i2}=0$  V, calcular

la v<sub>o</sub>.

Datos: NPN:  $h_{fe}=200$ ,  $h_{ie}=5k$ &,  $h_{oe}^{-1}=50k$ &,  $h_{re}=0$ ; PNP:  $h_{fe}=150$ ,  $h_{ie}=3k$ &,  $h_{oe}^{-1}=50k$ &,  $h_{re}=0$

Nota: Considerar únicamente el parámetro h<sub>oe</sub> en los transistores Q2, Q3, Q10 y Q11. En el resto se tomará como nulo.

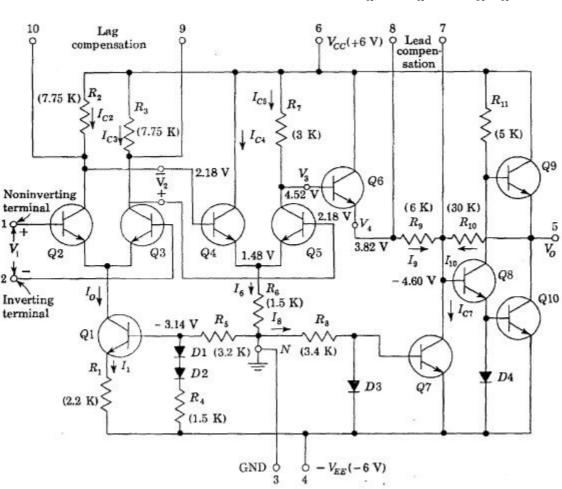

P6.10 Comprobar el valor de las tensiones indicadas en el esquema del amplificador operacional MC1530 de la figura P6.10.

Nota: Despreciar las intensidades de base.

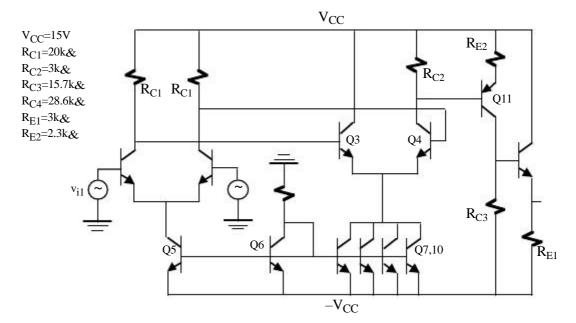

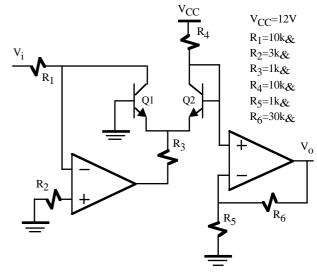

- **P6.11** La figura P6.11 muestra el esquema de un amplificador operacional sencillo. Se pide:

- a) Calcular las intensidades que circula por cada uno de los transistores y el valor de  $v_o$  en continua. Utilizar los principios de simetría de los amplificadores diferenciales. Despreciar la  $I_B$  frente a  $I_C$  ( $I_B << I_C$ ).

- b) Determinar la potencia de disipación de este circuito.

- c) Si los transistores Q1 y Q2 tienen una  $h_{FE}$ =100, calcular las corrientes de entrada.

Figura P6.9

d) Obtener el modelo equivalente en tensión del amplificador utilizando las aproximaciones que se consideren

### oportunas.

$\begin{aligned} &\text{Datos: NPN:} & \ h_{fe}\!\!=\!\!150, \ h_{ie}\!\!=\!\!5k\text{\&}, \ h_{oe}\!\!=\!\!h_{re}\!\!=\!\!0; \\ &\text{PNP: } h_{fe}\!\!=\!\!120, h_{ie}\!\!=\!\!4k\text{\&}, h_{oe}\!\!=\!\!h_{re}\!\!=\!\!0. \end{aligned}$

Figura P6.10

Figura P6.11

## **TEMA 7**

# Etapas de salida

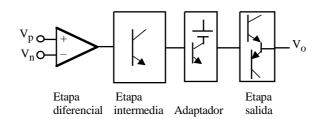

### 7.1.- Introducción

Las etapas de salida, también denominadas etapas de potencia, son configuraciones especiales localizadas a la salida de un amplificador utilizadas para proporcionar cierta cantidad de potencia a una carga con aceptables niveles de distorsión. Además, una etapa de salida debe ser independiente del propio valor de la carga, tener reducido consumo estático de potencia y no limitar la respuesta en frecuencia del amplificador completo.

Las etapas de salida son diseñadas para trabajar con niveles de tensión y corriente elevados. Las aproximaciones y modelos de pequeña señal no son aplicables o deben ser utilizados con mucho cuidado. Sin embargo, la linealidad de una etapa es una medida que proporciona la calidad del diseño, muchas veces caracterizada a través de la distorsión armónica total (total harmonic distortion o THD). Este parámetro es un valor eficaz o rms de las componentes armónicas de la señal de salida, sin incluir la fundamental de la entrada, expresada a través del porcentaje en términos de rms respecto a la fundamental. Los equipos de sonido de alta fidelidad tienen un THD inferior a 0.1%.

Otro parámetro importante de una etapa de potencia es su<u>eficiencia</u>, que indica el porcentaje de potencia entregada a la carga respecto de la potencia total disipada por la etapa. Un valor alto de eficiencia se traduce en una mayor duración del tiempo de vida de las baterías o en el uso de fuentes de alimentación de bajo coste, además de minimizar los problemas de disipación de potencia y coste del propio transistor de potencia. Es por ello, que las etapas de salida utilizan transistores de potencia (> 1W) y el uso de aletas refrigeradoras resulta en algunos casos imprescindible.

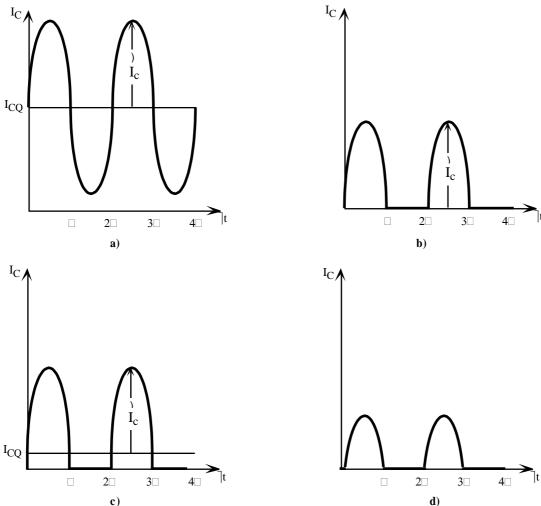

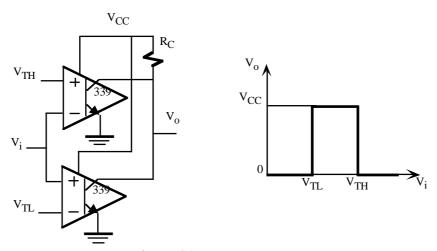

Las etapas de salida tradicionalmente son clasificadas de acuerdo a la forma de onda de la corriente de colector del transistor de salida en clase A, clase B, clase AB y clase C. La figura 7.1 ilustra esta clasificación. En la etapa clase A (figura 7.1.a), el transistor es polarizado con un corriente en continua de valor  $I_{CQ}$  mayor que la corriente de alterna de amplitud  $I_{c}$  de forma que el periodo de conducción es de 360°. En contraste, en la clase B (figura 7.1.b) la polarización DC es nula y sólo conduce en un semiperiodo de la señal de entrada (180°). Como se estudiará más tarde, existe otro transistor que estará activo en el siguiente semiperiodo alternando las fases. La etapa clase AB (figura 7.1.c), intermedio entre la A y la B, el transistor conduce un ángulo ligeramente superior a 180° y mucho menor que 360°. En la etapa clase C (figura 7.1.d) conduce ángulos inferiores a 180° y son empleadas usualmente en radiofrecuencia como por ejemplo teléfonos móviles y transmisores de radio y TV. Por sencillez, en este tema sólo se estudiarán las etapas de salida clase A, B y AB.

Figura 7.1. Clasificación de las etapas de salida: a) claseA, b) clase B, c) Clase AB y d) Clase C.

## 7.2.- Cálculos de potencia

En el análisis de etapas de salida es importante realizar cálculos de potencia. Los transistores tienen limitaciones sobre la cantidad de potencia que pueden suministrar o disipar, cuyo valor no debe superar un máximo establecido por el fabricante. A su vez, la etapa de salida debe proporcionar una determinada potencia a la carga.

• **Potencia promedio** (*average*). La potencia promedio suministrada o disipada por un circuito lineal o no lineal se define como

$$P = \frac{1}{}^{T}V(t)I(t)dt$$

(7.1)

siendo V(t) e I(t) la tensión y corriente que circula por el circuito y T el periodo. En la práctica, un amplificador tiene dos componentes: DC y AC (que por sencillez se considera del tipo sinusoidal). De esta manera, las tensiones y corrientes se pueden expresar como

$$V(t) = V_{DC} + v(t)$$

$$I(t) = I_{DC} + i(t)$$

(7.2)

Sustituyendo 7.2 en 7.1 resulta que la potencia promedio es

$$P = \frac{1}{T} + \frac{1}{0} \left( V_{DC} + v(t) \right) I_{DC} + i(t) dt = V_{DC} + V_{$$

puesto que las componentes v(t) e i(t) son sinusoidales con un valor promedio nulo, es decir,

$$\frac{1}{T} + \frac{T}{0} v(t) dt = \frac{1}{T} + \frac{T}{0} i(t) dt = 0$$

(7.4)

La ecuación 7.3 indica que la potencia promedio suministrada (o consumida) por un circuito tiene dos componentes, uno relativo a términos de corriente continua y otra a términos de corriente alterna, supuesto que las componentes de tensión e intensidad tienen valor promedio nulo.

La potencia promedio de una componente sinusoidal también puede expresarse en términos de valores eficaces como

$$\mathbf{r} = \mathbf{I}_{ef} \, \mathbf{v}_{ef} = \sqrt{\frac{1}{T}} + 0^{T} \mathbf{I}_{2}(\mathbf{t}) \mathbf{u} \sqrt{\frac{1}{T}} + 0^{T} \mathbf{v}_{2}(\mathbf{t}) \mathbf{u}$$

(7.5)

En el caso de que v(t) e i(t) sean señales sinusoidales, resulta que  $_{ef} = V_o/\sqrt{2}$  e  $I_{ef} = \frac{1}{o}/\sqrt{2}$ , siendo  $V_o$  e  $I_{o}$  las amplitudes. Por ejemplo, las tensión de 220 V de la red eléctrica es un valor eficaz que corresponde a una tensión pico de 220  $\sqrt{2}$ =311 V. Como resultado, la ecuación 7.5 se transforma en

$$P = I_{ef} V_{ef} = \frac{1}{2} \hat{I}_o \hat{V}_o$$

(7.6)

• **Potencia promedio entregada a una carga resistiva**. La potencia promedio entregada a una carga resistiva de valor R<sub>L</sub> suponiendo solamente componentes sinusoidales, se obtiene aplicando la ecuación 7.1

$$P = \frac{1}{v} v(t)i(t)dt = \frac{1}{v} R_{L}i^{2}(t)dt = \frac{1}{v} v^{2}(t) dt$$

(7.7)

Si se considera que la intensidad es sinusoidal,  $i(t) = \hat{j}_{t} \cos wt$ , la ecuación 7.7 se transforma en

$$P = \frac{1}{T} {}^{T} R_{L} \left( J_{c} \cos wt \right)^{2} dt = \frac{R_{L}}{T} {}^{T} \frac{\hat{I}_{o}^{2}}{2} (1 + \cos 2wt) dt = \frac{J_{c}^{2}}{2} R_{L}^{2} = \frac{1}{2} \hat{o} \hat{o} = \frac{2}{\sqrt{2}}$$

(7.8)

• Potencia promedio suministrada por una fuente de alimentación. Una fuente de alimentación mantiene la tensión constante (V<sub>CC</sub>) mientras la intensidad varía con el tiempo. Suponiendo corrientes sinusoidales, la potencia promedio suministrada por una fuente de alimentación viene dada por

$$P = \frac{1}{T} V_{CC} T_{I}(t) dt = T_{I} V_{CC} T_{DC} + i(t) dt = V_{CC} T_{DC}$$

(7.9)

es decir, solamente depende de sus componentes DC y es independiente de las corrientes en alterna.

• **Rendimiento**. El rendimiento (| ) se define como la relación entre la potencia promedio en alterna disipada por la resistencia de carga y la potencia suministrada por las fuentes de alimentación al circuito, y se expresa como

El rendimiento es un parámetro muy importante en las etapas de salida ya que proporcionan una medida del porcentaje de potencia suministrada por las fuentes de alimentación que es desviada a la carga. Su valor está comprendido  $0\delta$   $\delta$ 1. Un rendimiento bajo |<0.25 indica que la mayoría de la potencia es disipada por los dispositivos del circuito de forma que un porcentaje muy bajo se destina a la carga. Por el contrario, una valor alto (|>0.75) indica que la carga es el elemento que recibe mayor aportación de potencia.

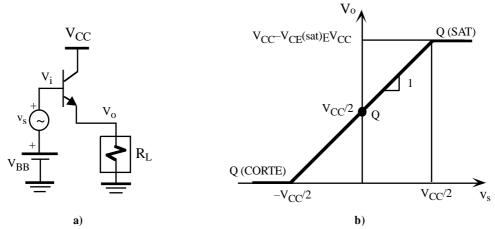

Figura 7.2. a) Etapa de salida clase A y b) curva de transferencia en tensión (VTC) referida a v<sub>c</sub>.

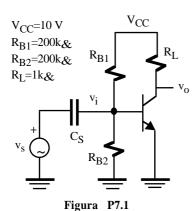

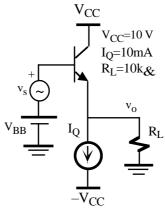

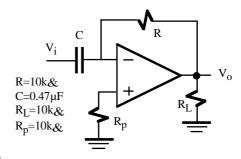

#### 7.3.- Etapa de salida clase A

La etapa de salida clase A más sencilla es el seguidor de emisor aunque su eficiencia es bastante baja (< 0.25). La figura 7.2.a muestra el esquema de este tipo de etapa polarizada con una fuente de tensión adicional ( $V_{BB}$ ) para que en ausencia de señal ( $v_s$ =0) la  $V_o$  sea  $V_{CC}$ /2; en este caso  $V_{BB}$ = $V_{CC}$ /2+ $V_{BE}$ . Es decir, la corriente de colector en continua de este transistor es

$$I_{CQ} = \frac{VCC}{2R_L} \tag{7.11}$$

La figura 7.2.b presenta su curva de transferencia en tensión (VTC) respecto a la señal de entrada  $v_s$ . Al tratarse de un seguidor de emisor la ganancia es ~1, luego la pendiente de la recta también es 1. Fácilmente se comprueba que la amplitud máxima de la tensión de salida es  $V_{CC}/2$  limitada por la tensión de alimentación y siempre que Q esté centrada sobre la recta de carga estática. La potencia de disipación promedio en alterna disipada por  $R_L$  se obtiene a partir de la ecuación 7.8

$$P_{L} = \frac{\hat{V}_{o}^{2}}{2R_{L}} \tag{7.12}$$

y esa potencia es máxima cuando  $V_{o}(max) = V_{CC}/2$  de forma que

$$P_{L}(\text{max}) = \frac{(V_{CC})^2}{8R_L}$$

(7.13)

La potencia suministrada por las fuentes de alimentación se obtienen a partir de la ecuación 7.9

$$P_{CC} = V_{BB}I_{BQ} + V_{CC}I_{CQ} \times V_{CC}I_{CQ} = \frac{(V_{CC})^2}{2R_L}$$

(7.14)

al ser  $I_{BQ} << I_{CQ}$  y sustituyendo  $I_{CQ}$  por la ecuación 7.11. La máxima eficiencia se determina por las ecuaciones 7.13 y 7.14

$$|_{\text{max}} = \frac{1}{P_{\text{CC}}} = \frac{1}{4}$$

(7.15)

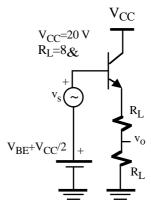

## 7.4.- Etapa de salida clase B (Push-Pull)

La mayor desventaja de la anterior etapa de salida es el consumo estático de potencia incluso en ausencia de señal de entrada. En muchas aplicaciones prácticas existen largos tiempos muertos (*standby*) a la espera de señal de entrada o con señales intermitentes como es el caso de voz humana. Etapas de salida que desperdician potencia en períodos *standby* tiene efectos perniciosos importantes. En primer lugar, se reducen drásticamente el tiempo de duración de las baterías de los equipos electrónicos. En segundo lugar, ese consumo de potencia continuado provoca un incremento de temperatura en los dispositivos que limitan su tiempo medio de vida dando lugar a una mayor probabilidad de fallar con el tiempo el sistema electrónico.

La etapa de salida clase B tiene consumo estático de potencia en modo *standby* prácticamente cero. Utiliza dos transistores, uno NPN y otro PNP, en contrafase que conducen alternativamente en función de si la señal de entrada es positiva o negativa. De ahí, el nombre de *push-pull*. Otra ventaja adicional es su mejor eficiencia que puede alcanzar un valor máximo próximo al 78% muy superior al 25% de la etapa de salida clase A.

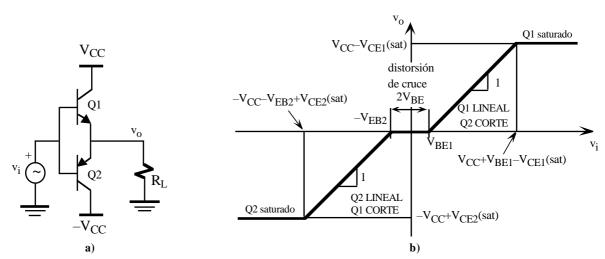

Figura 7.3. Etapa de salida clase B (push-pull): a) estructura básica y b) VTC.

En la figura 7.3.a se presenta la estructura básica de una etapa de salida clase B (*push-pull*). Utiliza transistores NPN y PNP que deben ser *complementarios*, es decir, de idénticas características para lograr una simetría en su modo de operación. Obsérvese como ambos transistores operan como seguidor de emisor con una ganancia en tensión muy próxima a 1.

La figura 7.3.b muestra la VTC de este circuito. Para  $v_i=0$ , ambos transistores se encuentran en corte ( $v_0=0$ ) y el consumo estático de corriente es nulo (modo standby). Si se incrementa la tensión de entrada hasta que O1 entra en conducción, v<sub>i</sub>>V<sub>BEI</sub>(on), entonces aparece niveles apreciables de corriente en Q1 que circularán por la resistencia de carga; en este caso Q2 está en corte al verificarse V<sub>BE2</sub>>0. A partir de ahora, Q1 opera en la región lineal hasta alcanzar la saturación ( $v_i > V_{CC} + V_{BE1} - V_{CE1}(sat)$ ). Similares resultados se obtienen para  $v_i < 0$  siendo ahora Q2 el transistor que entra en la región lineal con una tensión máxima de salida limitada por la región de saturación (v<sub>i</sub><-V<sub>CC</sub>-V<sub>EB2</sub>+V<sub>CE2</sub>(sat)), estando siempre Q1 en corte. Resumiendo, con v<sub>i</sub>>V<sub>BE1</sub>(on) Q1 está en conducción y Q2 en corte y con v<sub>i</sub><-V<sub>EB2</sub>(on) Q1 está en conducción y Q2 en corte. Además, existe una zona muerta -V<sub>EB2</sub>(on)<v<sub>i</sub> <V<sub>BE1</sub>(on) que ambos transistores están en corte. Esta característica introduce una distorsión de salida, denominada distorsión de cruce (crossover), cuyo efecto puede observarse claramente en la figura 7.4. En la curva de la izquierda se observa una señal de entrada con diferentes amplitudes y en la derecha la tensión de la salida. En el caso 1, una señal de entrada de amplitud pequeña resulta fuertemente distorsionada debido al rango de valores necesarios para que algún transistor entre en conducción (2V<sub>BE</sub>(on)). En el caso 2, al tener la señal de entrada suficiente amplitud este efecto es menos importante pero sigue existiendo un intervalo nulo de tensión en la salida cuando -V<sub>EB2</sub>(on)<v<sub>i</sub> <V<sub>BE1</sub>(on). El caso 3, una amplitud excesiva a la entrada origina recorte (clipping) a la salida; claramente se puede observar en la VTC de la figura 7.3.b los límites máximos de salida.

Figura 7.4. Salida de la etapa clase B push-pull para diferentes amplitudes de entrada.

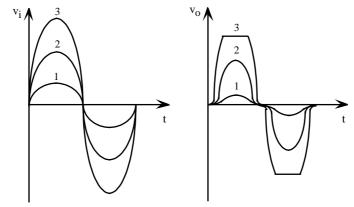

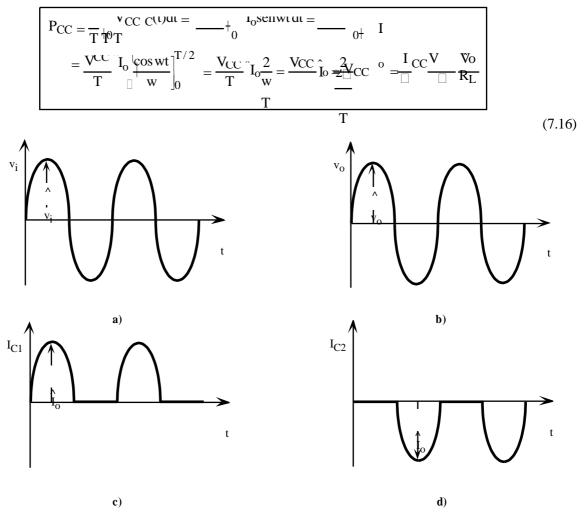

#### 7.4.1- Potencia de salida y eficiencia de la etapa clase B

A continuación se estudia la potencia y eficiencia de esta etapa suponiendo despreciable el efecto de distorsión de cruce, aproximación válida cuando las tensiones de alimentación son altas. En la figura 7.5 se muestran las formas de onda y corrientes de colector de la etapa clase B de la figura 7.3.a; estas corrientes definen a su vez las corrientes que suministra las fuentes de alimentación. Las corrientes de colector de los transistores tienen validez únicamente en un semiperiodo (periodo de conducción del transistor). Para obtener la potencia promedio suministrada por una fuente de alimentación es necesario utilizar la ecuación 7.9, resultando

Figura 7.5. Formas de onda. a) Tensión de entrada b) salida, c) Corriente de colector de Q1 y d) de Q2.

Puesto que cada fuente proporciona la misma magnitud de potencia, la potencia promedio total por ambas fuentes de alimentación es el doble de lo indicado en la ecuación 7.16 ( $2P_{CC}$ ).

La potencia promedio entregada a la carga es

$$P_{L} = \frac{1}{2} \frac{\hat{V}_{o}}{R_{L}}$$

$$(7.17)$$

Luego, la eficiencia de esta etapa

$$\frac{P_{L}}{2P_{CC}} = \frac{V_{O}}{4 V_{CC}}$$

(7.18)

Obsérvese cómo la eficiencia de esta etapa es independiente de  $R_L$  y varía linealmente con la amplitud de salida. La eficiencia máxima se produce para una amplitud máxima de la tensión de salida que es  $V_{CC}$ - $V_{CE}$ (sat) $EV_{CC}$ , resultando que

$$| \max = \frac{V}{\Box V_{CC} | CE(sat)} | H_{\Box} = 0.785 | (78.5\%)$$

$$| V_{CC} | V_{CC} |$$

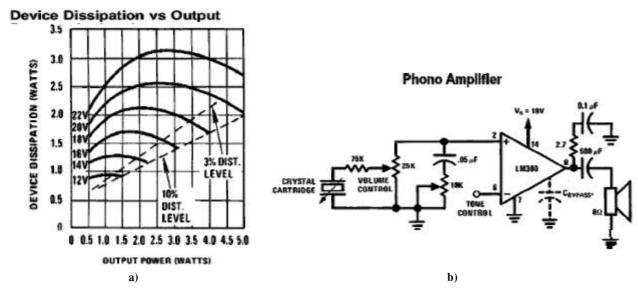

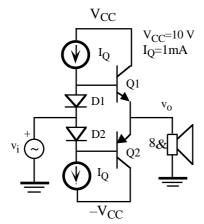

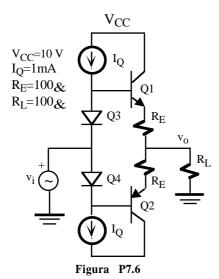

#### 7.5.- Etapa de salida clase AB (Push-Pull)

La distorsión de cruce característica de la etapa de salida clase B anterior puede ser eliminada añadiendo algún circuito que polarice a los transistores de salida con unas corrientes de polarización bajas, pero suficientes para que su punto de trabajo esté en la región lineal (próxima a la región de corte). Las figuras 7.6.a y 7.6.b presentan las configuraciones más utilizadas para polarizar los transistores de salida: con diodos y con un multiplicador  $V_{BE}$ .

Figura 7.6. Etapa clase AB con polarización por a) diodos y b) multiplicador V<sub>BE</sub>

• Polarización con diodos. La figura 7.6.a muestra la polarización basada en dos diodos. En ausencia de señal,  $v_i$ =0, la caída de tensión en diodo D1 hace que el transistor Q1 esté en la región lineal con una corriente de colector baja y lo mismo sucede a Q2 con el diodo D2; es decir, ambos transistores conducen. Cuando se aplica una tensión a la entrada uno de los transistores estará en la región lineal y el otro cortado, funcionando de una manera similar a la etapa clase B anterior pero con la ausencia de distorsión de cruce. En este caso la potencia promedio suministrada por una fuente de alimentación, utilizando la ecuación 7.16, es

$$P_{CC} = \frac{V_{CC}}{\Box} \frac{\hat{V}_{O}}{R_{L}} + I_{Q}V_{CC}$$

(7.20)

En general, el segundo término es despreciable frente al primero y el valor de la eficiencia indicada en las ecuaciones 7.18 y 7.19 siguen siendo válidas.

La polarización con diodos presenta una importante ventaja al proporcionar estabilización de la polarización con la temperatura. Al aumentar la temperatura, la  $V_{BE}$  de los transistores disminuye pero a su vez la caída de tensión de los diodos también lo que permite mantener constante la corriente de polarización de los transistores de salida.

• <u>Polarización con un multiplicador</u>  $V_{BE}$ . Otro procedimiento para obtener la diferencia de tensión  $2V_{BE}$  entre la base de los transistores necesaria para eliminar la distorsión de cruce es utilizar lo que se denomina un

multiplicador de  $V_{BE}$  mostrado en la figura 7.6.b. Este circuito consiste en un transistor (Q3) con dos resistencias ( $R_1$  y  $R_2$ ) conectadas entre su colector y emisor con la base. Si se desprecia la corriente de base (para ello  $R_1$  y  $R_2$  deben ser de unos pocos k&) entonces la corriente que circula por  $R_1$  es  $V_{BE3}/R_1$  y la tensión entre el colector y emisor de ese transistor es

$$V = \frac{V}{R_{\pm 3}} R_{D} + R \left(\frac{R_2}{R_1}\right)$$

$$(7.21)$$

es decir, la tensión  $V_{CE3}$  se obtiene multiplicando la  $V_{RE3}$  por un factor  $(1+R_1/R_2)$ .

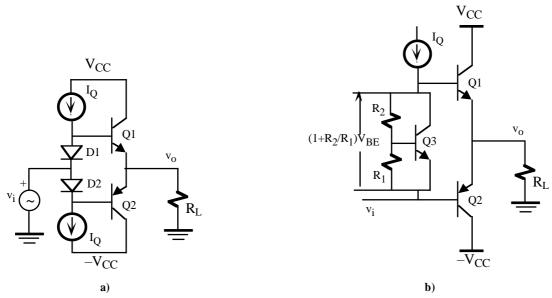

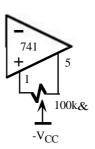

Figura 7.7. Ejemplo de la etapa clase B del amplificador operacional μA741: a) Estructura del circuito y b) VTC.

• Etapa de salida de un amplificador operacional. Como ejemplo práctico en la figura 7.7.a se muestra la estructura simplificada de la etapa de salida del amplificador operacional µA741 y su curva de transferencia en tensión. La tensión de entrada se aplica a la base de Q6 y la salida está formada por Q1 y Q2. Q3 polariza a Q4 y Q5 para eliminar la distorsión de cruce tal como se muestra en la VTC de la figura 7.7.b. Sin embargo, en ausencia de señal (v<sub>o</sub>=0) aparece una pequeña corriente (0.17mA) que circula por Q1 y Q2 al no estar totalmente en corte. (clase AB)

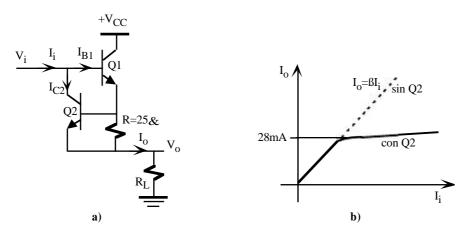

#### 7.6.- Protección contra sobrecarga

Una carga resistiva de salida muy baja, en el caso extremo un cortocircuito, puede dañar una etapa de salida. Para evitar este problema, a estas etapas se incorporan circuitos de protección que limitan la intensidad máxima de salida. En la figura 7.8.a se muestra un ejemplo típico de este circuito constituido por Q2 y R que limitan la intensidad  $I_o$  máxima de Q1. El funcionamiento es el siguiente. Para corrientes  $I_o$  bajas, el transistor Q2 está cortado ya que  $I_oR < V_{BE2@}$ ; en estas condiciones  $I_i = I_{B1}$  e  $I_o = \beta I_i$ . Q2 va a entrar en conducción cuando la caída de tensión en R es suficientemente alta para polarizar la unión base-emisor. Si Q2 conduce "roba" intensidad de base a Q1 porque ahora  $I_i = I_{C2} + I_{B1}$  o  $I_{B1} = I_i - I_{C2}$  siendo la intensidad de salida prácticamente constante de valor  $I_o = V_{BE2} / R_{H2} = I_o + I_{B1} + I_o + I_{B1} = I_o + I_{B1} =$

limitando la intensidad de salida alrededor de este valor.

**Figura 7.8. a)** Circuito de protección para limitar la intensidad de salida. **b)** Característica de transferencia entrada/salida de Q1 sin y con Q2.

#### 7.7.- Distorsión armónica

En un amplificador ideal la señal de salida es una réplica exacta de la señal de entrada. En amplificadores reales, debido a las características no lineales de los dispositivos, aparecen distorsiones que introducen modificaciones en las señales de salida. Entre los diferentes tipos de distorsiones, la distorsión armónica es uno de los más característicos. Por ejemplo, una señal pura a la entrada de 1kHz se transforma a la salida del amplificador con distorsión armónica en otra señal que además de tener la componente fundamental (1kHz) posee señales de armónicas de 2kHz (segundo armónico), 3kHz (tercer armónico), etc. Los analizadores de espectro son instrumentos que miden los armónicos presentes en señales y aplican técnicas basadas en el análisis de Fourier para descomponer las diferentes componentes frecuenciales. El analizador de formas de onda permite de una manera más precisa medir a través de técnicas de filtrado las componentes armónicas de una señal distorsionada. En las etapas de salidas clase AB y B, la distorsión es debida principalmente a los armónicos impares, siendo el tercer armónico el dominante.

La distorsión armónica total o THD (*Total Harmonic Distortion*) es un parámetro que mide la distorsión armónica que presenta una señala través de las componentes frecuenciales. El THD se define como

$$THD = \sqrt{D^2 + D_{32} + D_{44}^2 + \dots}$$

(7.22)

donde D2 es el cociente entre la amplitud del armónico de segundo orden y la amplitud de la componente fundamental,  $D_3$  es cociente entre la amplitud del armónico del tercer orden y la amplitud de la componente fundamental, ...

Cuando la distorsión armónica aparece en la salida, la potencia promedio calculado para la señal sin distorsionar  $(P_0)$  no es correcta. La potencia promedio total de una señal distorsionada se define como

$$P_{D} = P_{0}(1 + THD^{2})$$

(7.23)

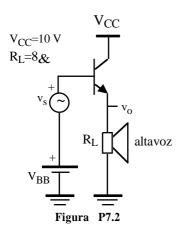

## 7.8.- Amplificadores de potencia integrados

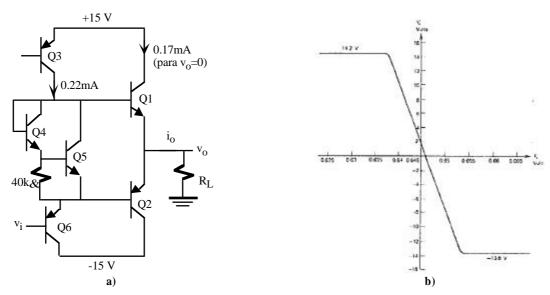

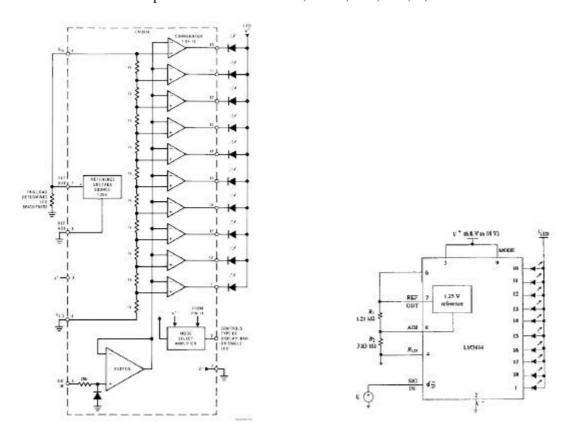

Existe en el mercado una gran variedad de amplificadores de potencia realizados en circuitos integrados. La mayoría de ellos consisten en una etapa amplificadora de alta ganancia seguida de una etapa de salida clase AB. El LM380 de National Semiconductor Corporation es ejemplo típico de un amplificador integrado de ganancia fija (50). Este amplificador ha sido diseñado para operar con tensiones de alimentación  $V_s$  entre 12-22 V, proporciona una potencia de de salida 2.5 W y tiene un consumo estático de potencia reducido de 0.13W a  $V_s$ =18V. La selección de  $V_s$  depende del valor de la resistencia de carga y la potencia requerida de salida. El fabricante proporciona curvas de la potencia de disipación del circuito con la potencia de salida para diferentes valores de  $V_s$  y resistencia de carga. La figura 7.9.a presenta una de esas curvas para una carga de 8 & ( carga típica de un altavoz) e incluye además las rectas correspondientes a una THD del 3% y 10%. La figura 7.9.b muestra una aplicación típica de este amplificador. Otro ejemplo de amplificador de potencia es el LH0101 de National Semiconductor fabricado en tecnología de película delgada capaz de proporcionar hasta 60 W de salida y con un ancho de banda de 300kHz.

**Figura 7.9.** a) Curva de disipación con la potencia de salida de amplificador de audio LM380 para diferentes valores de la tensión de alimentación. b) Aplicación típica de este amplificador.

#### 7.9.- Consideraciones térmico-ambientales

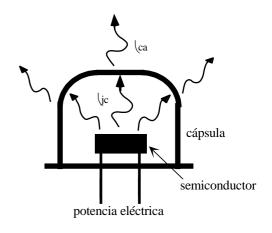

La potencia entregada a un dispositivo en forma de corriente eléctrica se transforma en calor. Este calor hace aumentar su temperatura que debe ser mantenida dentro de unos límites aceptables. Por ejemplo, la temperatura máxima que puede soportar las uniones de un semiconductor (diodos, transistores, etc ..) está comprendida entre 150 y 175 °C. La figura 7.10 describe gráficamente el sistema de conversión eléctrica en calor y su proceso de disipación. El semiconductor recibe corriente eléctrica que se transforma en calor. Este calor se transmite a la cápsula y ésta la radiará al exterior. Si la potencia disipada por el semiconductor es constante se alcanzará un equilibrio térmico

Figura 7.10. Radiación de calor.

estable después de un tiempo suficiente, siempre que no se deteriore el dispositivo.

Para medir la capacidad de eliminar el calor se introduce el concepto de *resistencia térmica* (generalmente representada por el símbolo \) como la resistencia que opone los materiales al paso de la transmisión de calor entre dos temperaturas. Como es evidente, una encapsulado metálico disipará más calor que uno de plástico por presentar menor resistencia térmica el primero que el segundo. El aumento de la temperatura de la unión de un semiconductor por encima de la temperatura de la cápsula está relacionado con la potencia disipada mediante la ecuación

$$T_j \quad T_c = P_j \setminus_{jc} \tag{7.24}$$

donde  $T_j$  es la temperatura en °C de la unión del semiconductor,  $T_c$  es la temperatura en °C de la cápsula,  $P_j$  es la potencia eléctrica en W y  $\setminus_{jc}$  es la resistencia térmica en °C/W entre la unión y la cápsula. Esta resistencia térmica es función del tipo de semiconductor y cápsula (plástico, cerámico, metálica,...) y es especificada por el fabricante. La temperatura de la cápsula se transmite a su vez al exterior. El aumento de la temperatura de la cápsula por encima de la temperatura ambiente  $(T_a)$  se expresa mediante la ecuación

$$T_c \quad T_a = P_j \setminus_{ca}$$

(7.25)

siendo  $\$  la resistencia térmica entre la cápsula y el exterior. La relación entre la potencia eléctrica absorbida por la unión, su temperatura y la temperatura ambiente se obtiene combinando las ecuaciones 7.24 y 7.25 resultando que

$$T_j \quad T_a = P_j \left( \downarrow_{jc} + \downarrow_{ca} \right) = P_j \setminus_{ja}$$

(7.26)

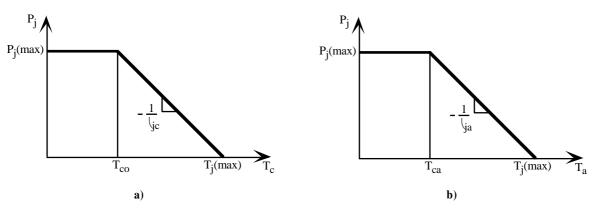

Figura 7.11. Curvas de degradación: a) de la temperatura de la cápsula; b) de la temperatura ambiente.

El fabricante suele proporcionar dos tipos de resistencia

- 1) \( \ja \) 0 R<sub>thj-a</sub> o resistencia térmica entre la unión y el ambiente. Resistencia térmica propia del transistor que incluye la resistencia térmica de la cápsula-ambiente.

- 2)  $\setminus_{ic}$  o  $R_{thi-c}$  o resistencia térmica entre la unión y la cápsula.

Ambos parámetros se expresan también a través de las curvas de degradación tal como se muestran en las gráficas de figura 7.11. Indican la máxima disipación de potencia admisible para una temperatura de cápsula

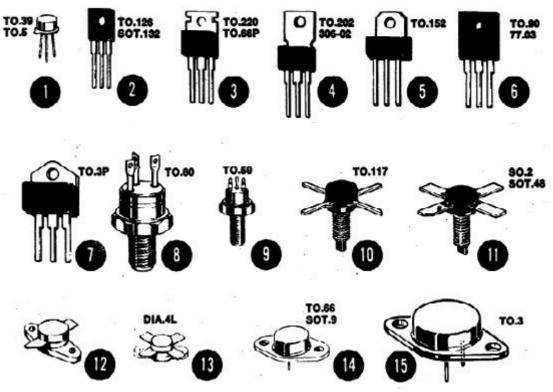

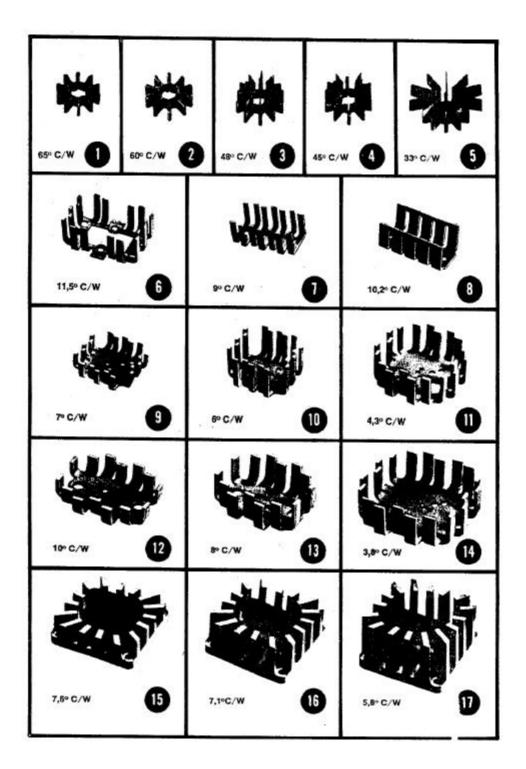

(figura 7.11.a) o para una temperatura ambiente (figura 7.11.b). Estas curvas se obtienen a partir de las ecuaciones 7.24 y 7.25 limitadas por la potencia máxima ( $P_j(max)$ ) de disipación del dispositivo y la temperatura máxima ( $T_j(max)$ ) que puede alcanzar la unión. La figura 7.12 presenta diferentes tipos de encapsulados utilizados por el fabricante y la tabla 7.1 sus correspondientes resistencias térmicas  $l_{jc}$  y  $l_{ja}$ . Los transistores de potencia tienen encapsulados tipo TO.3 de baja  $l_{ja}$  a diferencia de los de baja potencia que usan encapsulados de mayor resistencia térmica. Como es evidente, es coste de un encapsulado es inversamente proporcional a su resistencia térmica.

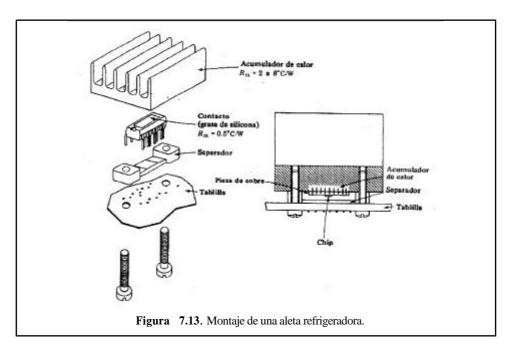

La disminución de la resistencia térmica de los dispositivos se realiza utilizando aletas refrigeradoras, también denominados radiadores, que se adhieren al dispositivo a través de mica o pasta de silicona. En la figura 7.13 se presenta el sistema de fijación de una aleta a un dispositivo. La ecuación de disipación de calor en este tipo de estructuras es

$$T_{j} \quad T_{a} = P_{j}(\downarrow_{jc} + \downarrow_{cr} + \downarrow_{ra})$$

$$(7.27)$$

Figura 7.12. Diferentes tipos de encapsulados.

| Tipo de contenedor      | ∖ <sub>jc</sub> o R <sub>thj-c</sub> | ∖ <sub>ja</sub> o R <sub>thj-a</sub> |

|-------------------------|--------------------------------------|--------------------------------------|

| TO5-TO.39               | 10 a 60 °C/W                         | 175 a 220 °C/W                       |

| TO.202                  | 12 a 15 °C/W                         | 60 a 90 °C/W                         |

| TO.126-SOT.32           | 3 a 15 °C/W                          | 80 a 100 °C/W                        |

| TO.220-T0.66 (Plástico) | 1.5 a 4.2 °C/W                       | 60 a 70 ℃/W                          |

| TO.3 (Plástico)         | 1 a 2 °C/W                           | 35 a 45 ℃/W                          |

| TO.66-SOT.9             | 4 a 5 °C/W                           | 75 a 85 °C/W                         |

| TO.59-TO.60             | 1.5 a 3 °C/W                         | 70 a 90 ℃/W                          |

| TO.3                    | 0.8 a 3 °C/W                         | 30 a 40 °C/W                         |

| TO.117                  | 15 a 35 °C/W                         | 70 a 90 ℃/W                          |

| SOT.48-SOE.2            | 1.8 a 6 °C/W                         | 40 a 70 ℃/W                          |

| DIAL.4L                 | 1.25 a 5.6 °C/W                      | 40 a 70 °C/W                         |

**Tabla 7.1**. Resistencias térmicas para los encapsulados de la figura 7.13.

| Tipo contenedor | Contacto directo | Contacto directo<br>más pasta de<br>silicona | Contacto con mica | Contacto con mica<br>más pasta de<br>silicona |

|-----------------|------------------|----------------------------------------------|-------------------|-----------------------------------------------|

| TO.39-TO.5      | 1                | 0.7                                          | -                 | =                                             |

| TO.126          | 1.4              | 1                                            | 2                 | 1.5                                           |

| TO.220          | 0.8              | 0.5                                          | 1.4               | 1.2                                           |

| TO.202          | 0.8              | 0.5                                          | 1.4               | 1.2                                           |

| TO.152          | 0.8              | 0.5                                          | 1.4               | 1.2                                           |

| TO.90           | 0.5              | 0.3                                          | 1.2               | 0.9                                           |

| TO.3 (Plástico) | 0.4              | 0.2                                          | 1                 | 0.7                                           |

| TO.59           | 1.2              | 0.7                                          | 2.1 1.5           |                                               |

| TO.117          | 2                | 1.7                                          | -                 |                                               |

| SOT.48          | 1.8              | 1.5                                          | -                 | -                                             |

| DIAL.4L         | 1.1              | 0.7                                          | -                 | -                                             |

| TO.66           | 1.1              | 0.65                                         | 1.8               | 1.4                                           |

| TO.3            | 0.25             | 0.12                                         | 0.8               | 0.4                                           |

**Tabla 7.2.** Resistencias térmicas capsula-aleta para diferentes tipos de aislante (en °C/W).

Figura 7.14. Diferentes tipos de aletas refrigeradoras.

Por último, el diseñador puede escoger la aleta refrigeradora más adecuada en función de las necesidades de potencia. En la figura 7.14 se presentan las más típicas. Suelen ser fabricados de aluminio ennegrecido para favorecer la disipación de calor. Las de mayor tamaño presentan menor resistencia térmica pero, a su vez, el precio es mayor. A veces, se añade a estas aletas un ventilador con objeto de producir aire en movimiento que refrigere las aletas.

## 7.10.- Dispositivos de potencia

#### 7.10.1.- Transistores bipolares de potencia

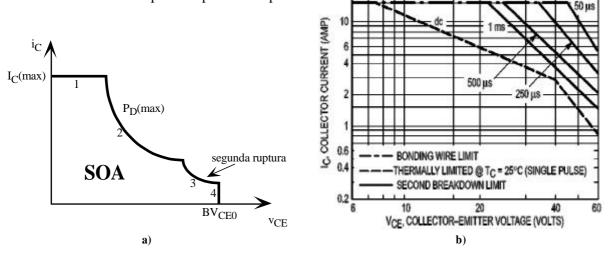

Los transistores BJT de potencia están diseñados para soportar niveles de tensión y corriente elevados y tienen una estructura física bastante diferente en comparación con los transistores de pequeña señal. La unión colector-base tiene gran área y el colector está fijado al encapsulado metálico para reducir su resistencia térmica. Los fabricantes proporcionan una zona de operación segura o SOA (*safe operating area*) para evitar el deterioro del dispositivo por efecto Joule. La figura 7.15.a indica esta zona dentro de las características i<sub>C</sub>,v<sub>CE</sub> del transistor en donde distinguen cuatro zonas limítrofes:

- 1 La corriente máxima del colector está limitada por los cables de conexión al encapsulado.

- 2 Hipérbola de disipación máxima definida por v<sub>CE</sub>i<sub>C</sub>=P<sub>D</sub>(max).

- 3 Fenómenos de segunda ruptura debido a la no uniformidad en la corrientes de la unión emisor-base que originan zonas de alta temperatura y deriva térmica que destruyen esa unión.

- 4 Ruptura de la unión colector-emisor.

El fabricante proporciona la zona SOA en escala logarítmica de forma que las curvas se transforman en rectas. Un ejemplo de esta gráfica aparece en la figura 7.15.b extraída de las características del 2N3055. Las diferentes curvas se obtienen aplicando pulsos no repetitivos de una duración determinada.

**Figura 7.15. a**) Regíon SOA de un transistor bipolar de potencia. **b**) SOA en escala logarítmica para el transistor de potencia NPN 2N3055.

Las principales diferencias de un transistor bipolar de potencia con respecto a un transistor de pequeña señal son:

- 1.- A corrientes muy altas, la ecuación de Ebers-Moll en la región lineal es I<sub>C</sub>=I<sub>S</sub>exp(V<sub>BF</sub>/2V<sub>T</sub>).

- 2.- La h<sub>FE</sub> es típicamente baja, entre 30 y 80, pudiendo llegar incluso a 5.

- 3.- La h<sub>ie</sub> es más pequeña que la resistencia de difusión de los terminales. Los modelos de pequeña señal no son válidos.

- 4.- La  $f_{\rm T}$  es baja, unos pocos MHz.

- 5.- La  $I_{CBO}$  es alta ( $\mu A$ ) y se dobla cada 10°C.

- 6.- la BV<sub>CE0</sub> está entre 50 y 60 V, pudiendo alcanzar valores de 500 V.

- 7.- I<sub>C</sub>(max) es del orden de amperios llegando incluso a 100A.

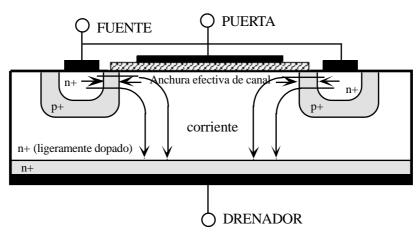

#### 7.10.2.- Transistores MOS de potencia

Los transistores MOS de potencia, similar a los transistores bipolares anteriores, son capaces de manejar niveles de tensión y corrientes elevados. Los transistores MOS de pequeña señal tienen una estructura incompatible para aplicaciones de potencia. Por ello, ha surgido una estructura muy popular basado en transistores MOS de enriquecimiento conocido como DMOS o de doble difusión MOS (double-diffused vertical MOS transistor) mostrado en la figura 7.16. La corriente controlada por la tensión de la puerta fluye desde las dos fuentes hasta el drenador a través del substrato ligeramente dopado. Los transistores DMOS son de canal estrecho pero poseen tensiones de rupturas de hasta 600 V y son capaces de manejar corrientes de 50 A. Este dispositivo se ha impuesto al V-groove MOS de la década de los 80 salvo, quizás, en aplicaciones de alta frecuencia.

Figura 7.16. Estructura física de un transistor vertical de alta potencia MOS (DMOS) de doble difusión.

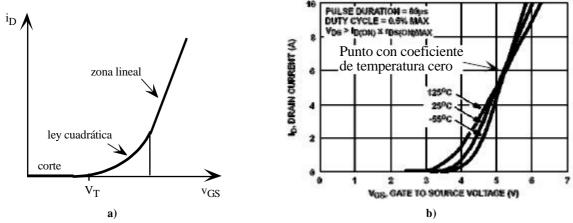

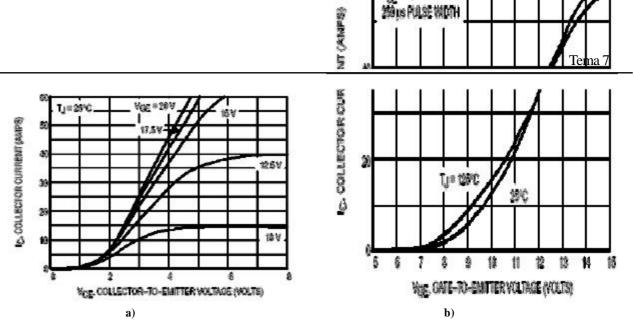

Una característica del DMOS es la relación lineal entre la corriente de drenador y la tensión de puerta cuando se alcanza la velocidad de saturación. Este fenómeno se produce cuando los portadores móviles alcanzan una velocidad límite debido al elevado campo eléctrico a lo largo del canal estrecho. La figura 7.17.a describe la relación  $i_D$ - $v_{GS}$  de un transistor DMOS. Se distinguen tres regiones: corte cuando la  $v_{GS}$ - $v_{T}$ , ley cuadrática en la cual la relación entre  $i_D$  y  $v_{GS}$  sigue la ecuación cuadrática clásica de un transistor MOS y lineal que debido a la velocidad de saturación existe una relación lineal entre la  $i_D$  y  $v_{GS}$  utilizada para amplificación. Otro aspecto importante de los DMOS es la variación de sus características con la temperatura. Un ejemplo es la curva  $i_D$ - $v_{GS}$  del transistor DMOS IRF 630 de Siliconix mostrada en la figura 7.17.b. Existe un punto alrededor de  $v_{GS}$ =5.4V en donde la intensidad  $i_D$  es insensible con la temperatura conocido como punto con coeficiente de temperatura cero; tensiones inferiores a ese punto el transistor presenta un coeficiente térmico positivo y superiores negativo. Por ello, los transistores DMOS no sufren de deriva térmica para tensiones de polarización superiores a ese valor.

Por último, los transistores DMOS comparados con los bipolares de potencia presentan una serie de ventajas. Los DMOS carecen de fenómenos de segunda ruptura que limitan la SOA de los bipolares (figuras 7.15.a y 7.15.b) y no requieren corrientes de polarización elevados (son dispositivos controlados por tensión). No obstante, las capacidades asociadas a sus terminales son altas que precisan de etapas amplificadoras previas capaces de cargar y descargar esas capacidades a una velocidad adecuada. Sin embargo, al ser los DMOS más rápidos que los bipolares se utilizan en aplicaciones de conmutación como, por ejemplo, circuitos de control de motores.

Figura 7.17. a) Característica. i<sub>D</sub>-v<sub>GS</sub> de un DMOS. b) Característica. i<sub>D</sub>-v<sub>GS</sub> con la temperatura del RF630.

## 7.10.3.- Transistores IGBT's

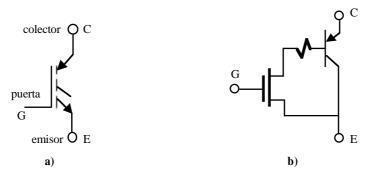

El IGBT o *insulated gate bipolar transistor* es dispositivo triterminal - puerta, emisor y colector-que reune las características de los transistores bipolares y FET siendo capaz de controlar grandes potencias (1MVA) con tensiones de puerta relativamente bajas (12 V a 15 V) y frecuencias de conmutación elevadas (500kHz). La combinación de una SOA muy amplia, alta velocidad y baja tensión de saturación les hace idóneos para aplicaciones de control de grandes potencias como es el control de motores, equipos de soldadura, etc.

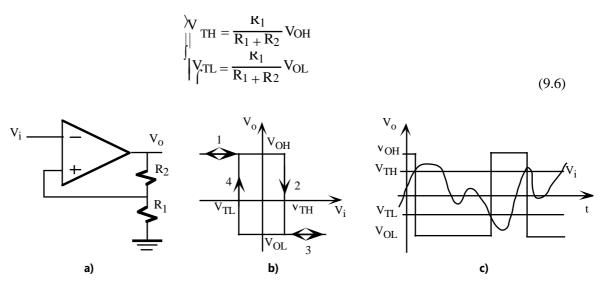

Figura 7.19. a) Símbolo del IGBT y b) modelo eléctrico equivalente simplificado.